# The Application of Programmable DSPs in Mobile Communications

# The Application of Programmable DSPs in Mobile Communications

Edited by

Alan Gatherer and Edgar Auslander Both of Texas Instruments Inc., USA

Copyright © 2002 by John Wiley & Sons, Ltd Baffins Lane, Chichester, West Sussex, PO19 1UD, England National 01243 779777 International (+44) 1243 779777

e-mail (for orders and customer service enquiries): cs-books@wiley.co.uk Visit our Home Page on http://www.wiley.co.uk or http://www.wiley.com

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency, 90 Tottenham Court Road, London, W1P 9HE, UK, without the permission in writing of the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the publication.

Neither the author(s) nor John Wiley & Sons Ltd accept any responsibility or liability for loss or damage occasioned to any person or property through using the material, instructions, methods or ideas contained herein, or acting or refraining from acting as a result of such use. The author(s) and Publisher expressly disclaim all implied warranties, including merchantability of fitness for any particular purpose.

Designations used by companies to distinguish their products are often claimed as trademarks. In all instances where John Wiley & Sons is aware of a claim, the product names appear in initial capital or capital letters. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

# Other Wiley Editorial Offices

John Wiley & Sons, Inc., 605 Third Avenue, New York, NY 10158-0012, USA

WILEY-VCH Verlag GmbH Pappelallee 3, D-69469 Weinheim, Germany

John Wiley & Sons Australia Ltd, 33 Park Road, Milton, Queensland 4064, Australia

John Wiley & Sons (Canada) Ltd, 22 Worcester Road Rexdale, Ontario, M9W 1L1, Canada

John Wiley & Sons (Asia) Pte Ltd, 2 Clementi Loop #02-01, Jin Xing Distripark, Singapore 129809

#### British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

ISBN 0471 48643 4

Typeset in Times by Deerpark Publishing Services Ltd, Shannon, Ireland. Printed and bound in Great Britain by T. J. International Ltd, Padstow, Cornwall.

This book is printed on acid-free paper responsibly manufactured from sustainable forestry, in which at least two trees are planted for each one used for paper production.

# Contents

| Biographies                                                                                                                                            | xiii   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| List of Contributors                                                                                                                                   | xv     |

| 1 Introduction                                                                                                                                         | 1      |

| Edgar Auslander and Alan Gatherer                                                                                                                      | _      |

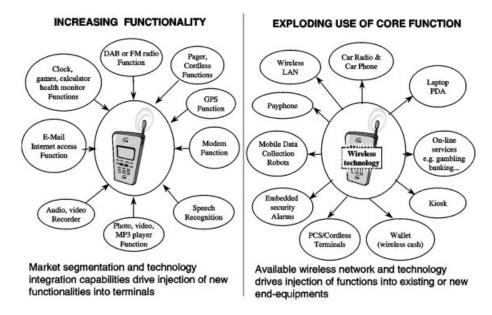

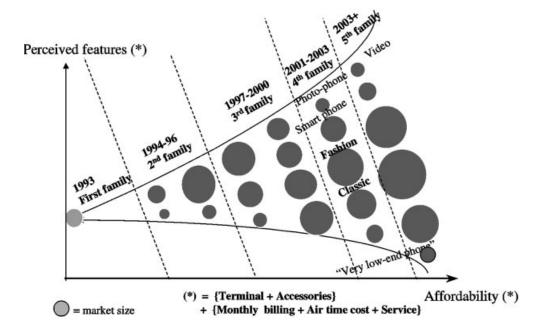

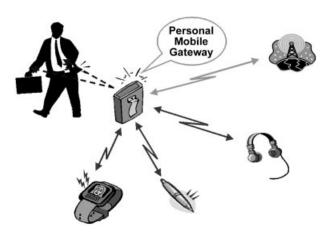

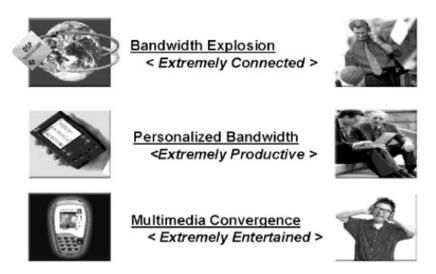

| 1.1 It's a Personal Matter                                                                                                                             | 2      |

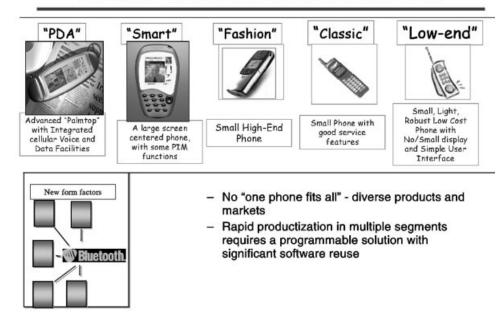

| 1.2 The Super Phone?                                                                                                                                   | 3      |

| 1.3 New Services                                                                                                                                       | 6      |

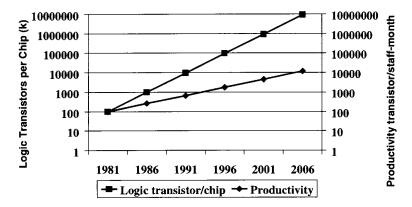

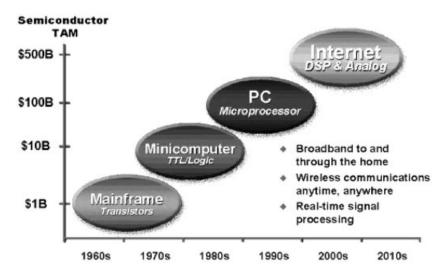

| 1.4 The Curse and Opportunity of Moore's Law 1.5 The Book                                                                                              | 8<br>9 |

| 2 The History of DSP Based Architectures in Second Generation Cellular Handsets  Alan Gatherer, Trudy Stetzler and Edgar Auslander                     | 11     |

| 2.1 Introduction                                                                                                                                       | 11     |

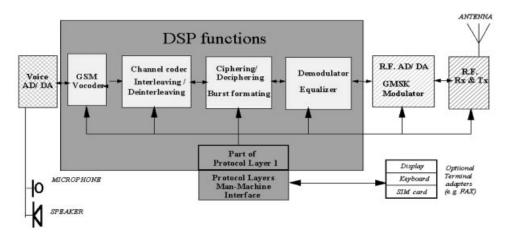

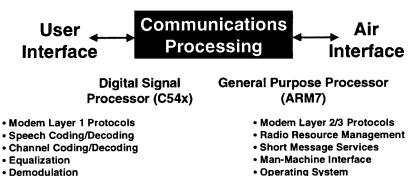

| 2.2 A History of Cellular Standards and Wireless Handset Architectures                                                                                 | 11     |

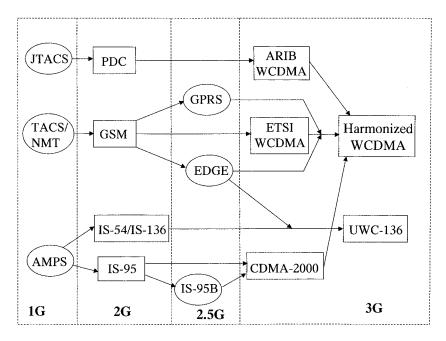

| 2.2.1 1G and 2G Standards                                                                                                                              | 11     |

| 2.2.2 2.5G and 3G Standards                                                                                                                            | 12     |

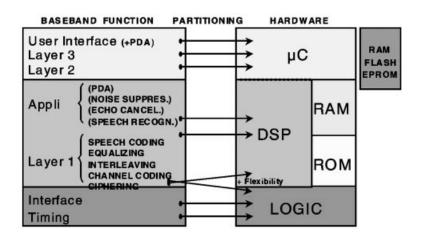

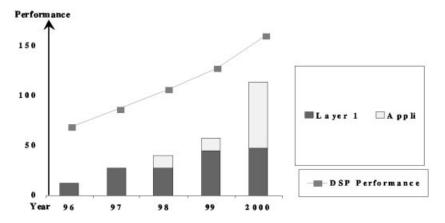

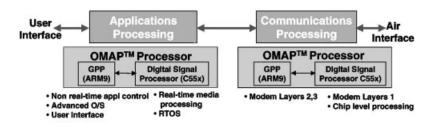

| 2.2.3 Architecture Evolution                                                                                                                           | 14     |

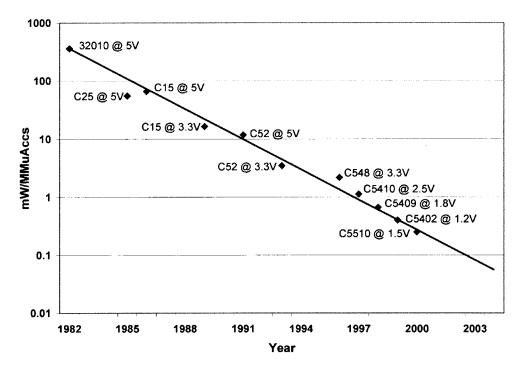

| 2.3 Trends in Low Power DSPs                                                                                                                           | 17     |

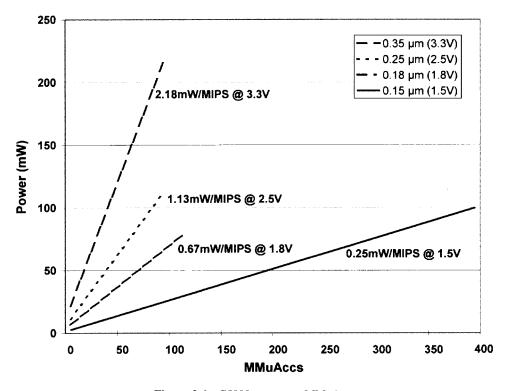

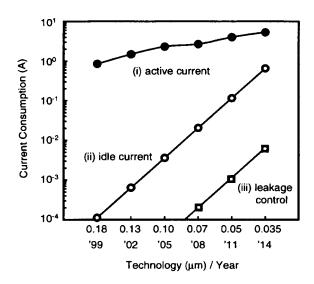

| 2.3.1 Process Improvement                                                                                                                              | 17     |

| 2.3.2 Instruction Set Enhancement                                                                                                                      | 19     |

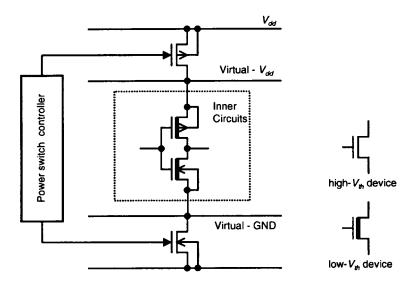

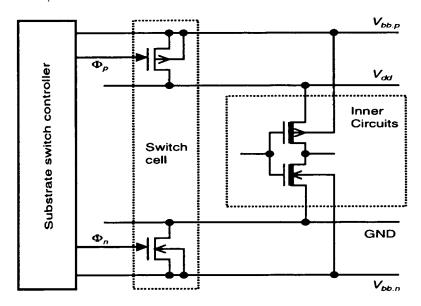

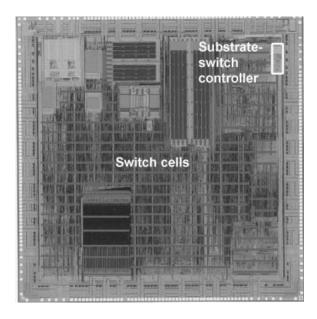

| 2.3.3 Power Management                                                                                                                                 | 21     |

| References                                                                                                                                             | 21     |

| 3 The Role of Programmable DSPs in Dual Mode (2G and 3G) Handsets<br>Chaitali Sengupta, Nicolas Veau, Sundararajan Sriram, Zhenguo Gu and Paul Folacci | 23     |

| 3.1 Introduction                                                                                                                                       | 23     |

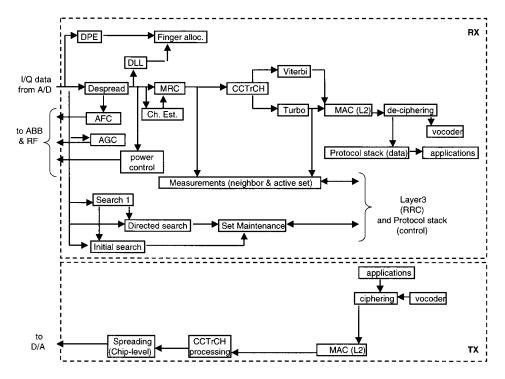

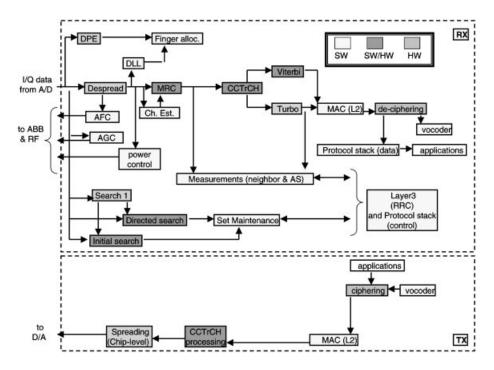

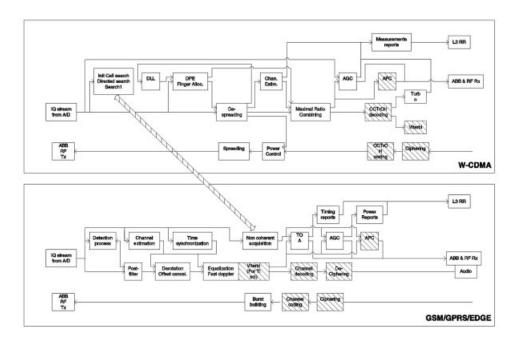

| 3.2 The Wireless Standards                                                                                                                             | 24     |

| 3.3 A Generic FDD DS Digital Baseband (DBB) Functional View                                                                                            | 25     |

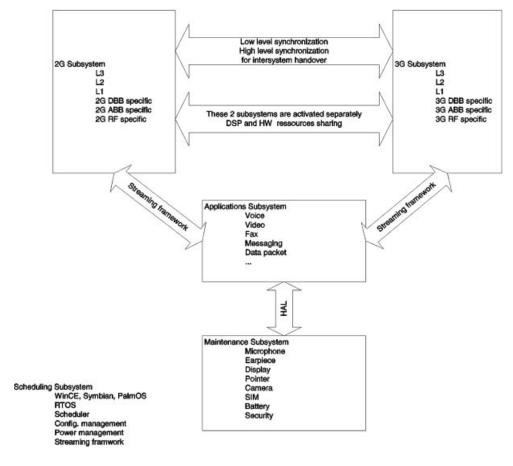

| 3.4 Functional Description of a Dual-Mode System                                                                                                       | 28     |

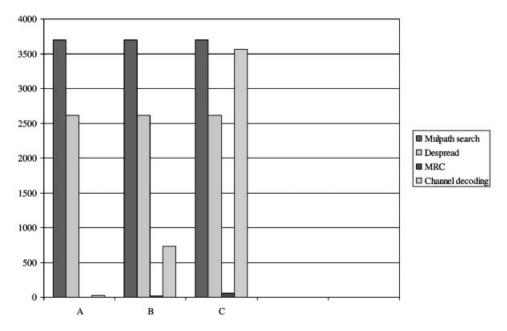

| 3.5 Complexity Analysis and HW/SW Partitioning                                                                                                         | 29     |

| 3.5.1 2G/3G Digital Baseband Processing Optimized Partitioning                                                                                         | 31     |

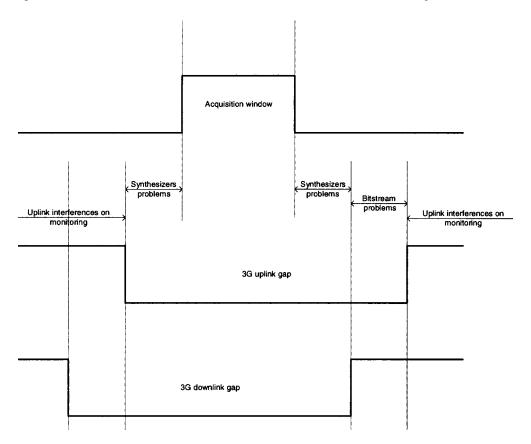

| 3.6 Hardware Design Approaches                                                                                                                         | 32     |

| 3.6.1 Design Considerations: Centralized vs. Distributed Architectures                                                                                 | 32     |

| 3.6.2 The Coprocessor Approach                                                                                                                         | 33     |

| 3.6.3 Role of DSP in 2G and Dual-Mode                                                                                                                  | 37     |

| 3.7 Software Processing and Interface with Higher Layers                                                                                               | 38     |

| 3.8 Summary                                                                                                                                            | 39     |

| 3.9 Abbreviations                                                                                                                                      | 39     |

| References                                                                                                                                             | 40     |

vi Contents

| 4 Programmable DSPs for 3G Base Station Modems                                            | 41  |

|-------------------------------------------------------------------------------------------|-----|

| Dale Hocevar, Pierre Bertrand, Eric Biscondi, Alan Gatherer, Frank Honore, Armelle Laine, |     |

| Simon Morris, Sriram Sundararajan and Tod Wolf                                            |     |

| 4.1 Introduction                                                                          | 41  |

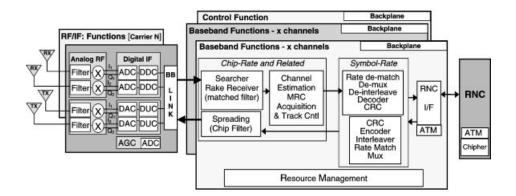

| 4.2 Overview of 3G Base Stations: Requirements                                            | 42  |

| 4.2.1 Introduction                                                                        | 42  |

| 4.2.2 General Requirements                                                                | 42  |

| 4.2.3 Fundamental CDMA Base Station Base Band Processing                                  | 43  |

| 4.2.4 Symbol-Rate (SR) Processing                                                         | 44  |

| 4.2.5 Chip-Rate (CR) Processing                                                           | 44  |

| 4.3 System Analysis                                                                       | 46  |

| 4.3.1 SR Processing Analysis                                                              | 46  |

| 4.3.2 CR Processing Analysis                                                              | 46  |

| 4.4 Flexible Coprocessor Solutions                                                        | 48  |

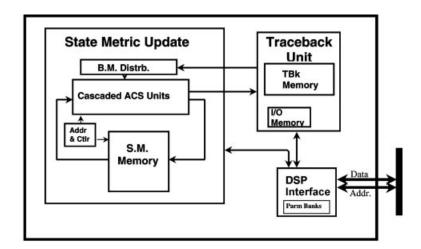

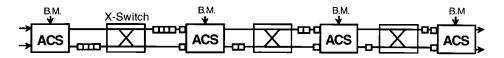

| 4.4.1 Viterbi Convolutional Decoder Coprocessor                                           | 48  |

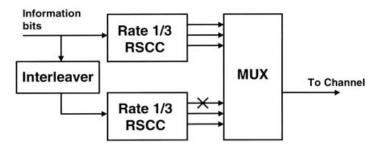

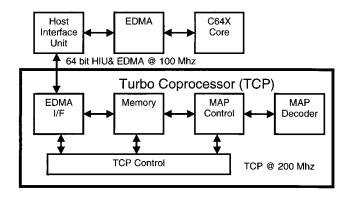

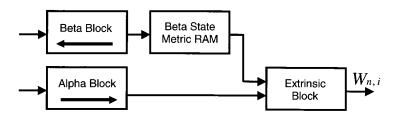

| 4.4.2 Turbo Decoder Coprocessor                                                           | 50  |

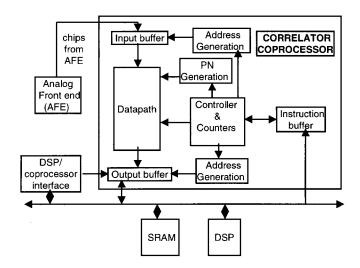

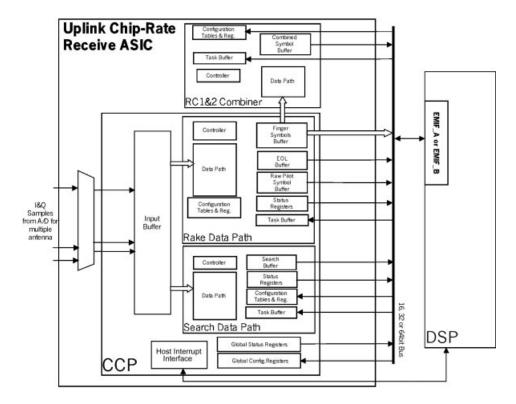

| 4.4.3 Correlator Coprocessor                                                              | 52  |

| 4.5 Summary and Conclusions                                                               | 54  |

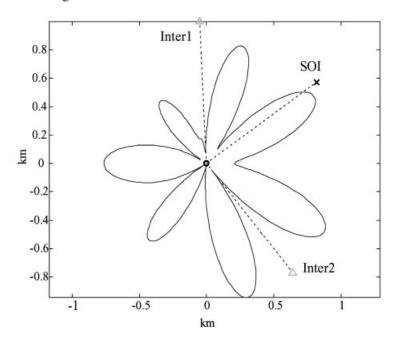

| 5 The Use of Programmable DSPs in Antenna Array Processing                                | 57  |

| Matthew Bromberg and Donald R. Brown                                                      |     |

| 5.1 Introduction                                                                          | 57  |

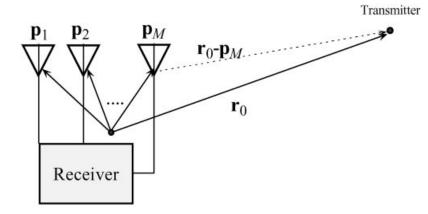

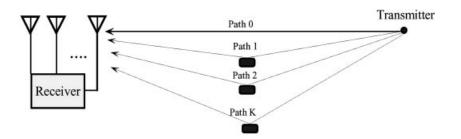

| 5.2 Antenna Array Signal Model                                                            | 58  |

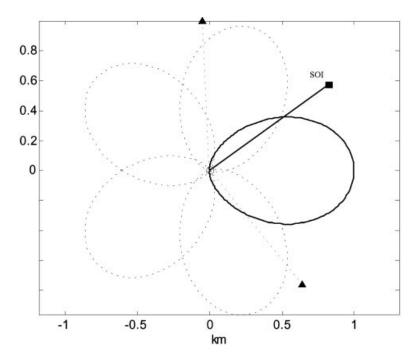

| 5.3 Linear Beamforming Techniques                                                         | 62  |

| 5.3.1 Maximum Likelihood Derivation                                                       | 62  |

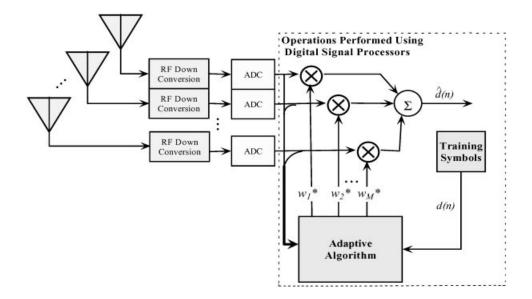

| 5.3.2 Least Mean Square Adaptation                                                        | 66  |

| 5.3.3 Least Squares Processing                                                            | 67  |

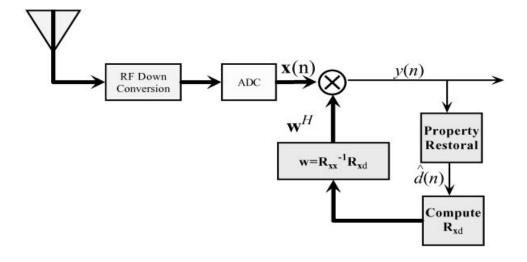

| 5.3.4 Blind Signal Adaptation                                                             | 71  |

| 5.3.5 Subspace Constraints                                                                | 73  |

| 5.3.6 Exploiting Cyclostationarity                                                        | 75  |

| 5.3.7 Transmit Beamformer Techniques                                                      | 77  |

| 5.4 Multiple Input Multiple Output (MIMO) Signal Extraction                               | 83  |

| 5.4.1 MIMO Linear System Model                                                            | 83  |

| 5.4.2 Capacity of MIMO Communication Channels                                             | 86  |

| 5.4.3 Linear Estimation of Desired Signals in MIMO Communication Systems                  | 87  |

| 5.4.4 Non-linear Estimation of Desired Signals in MIMO Communication Systems              | 90  |

| 5.4.5 Conclusions                                                                         | 93  |

| References                                                                                | 93  |

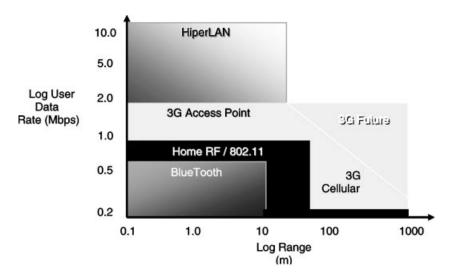

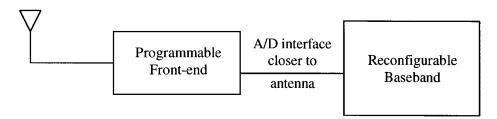

| 6 The Challenges of Software-Defined Radio                                                | 97  |

| Carl Panasik and Chaitali Sengupta                                                        | ,,  |

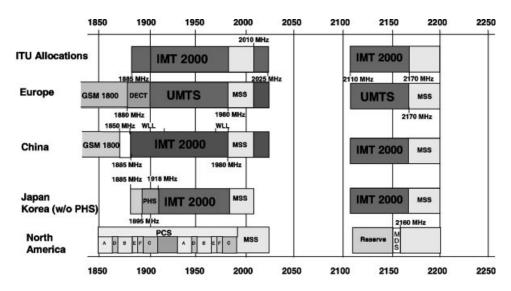

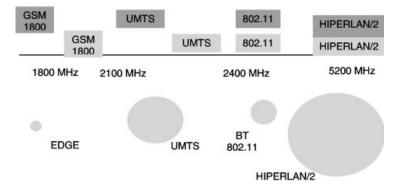

| 6.1 Cellular Communications Standards                                                     | 98  |

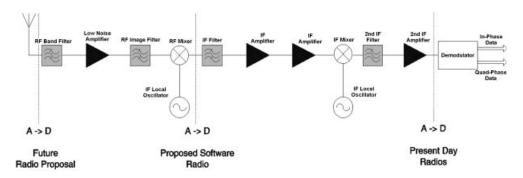

| 6.2 What is SDR?                                                                          | 98  |

| 6.3 Digitizing Today's Analog Operations                                                  | 101 |

| 6.4 Implementation Challenges                                                             | 103 |

| 6.5 Analog and ADC Issues                                                                 | 103 |

| 6.6 Channel Filter                                                                        | 104 |

| 6.7 Delta-Sigma ADC                                                                       | 104 |

| 6.8 Conclusion                                                                            | 105 |

| References                                                                                | 105 |

Contents vii

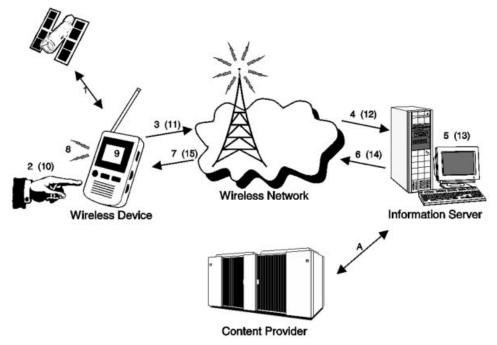

| 7 Enabling Multimedia Applications in 2.5G and 3G Wireless Terminals: Challenges and                |            |  |

|-----------------------------------------------------------------------------------------------------|------------|--|

| Solutions                                                                                           | 107        |  |

| Edgar Auslander, Madhukar Budagavi, Jamil Chaoui, Ken Cyr, Jean-Pierre Giacalone,                   |            |  |

| Sebastien de Gregorio, Yves Masse, Yeshwant Muthusamy, Tiemen Spits and Jennifer Webb               |            |  |

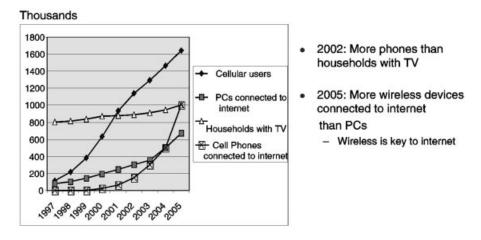

| 7.1 Introduction                                                                                    | 107        |  |

| 7.1.1 "DSPs take the RISC"                                                                          | 107        |  |

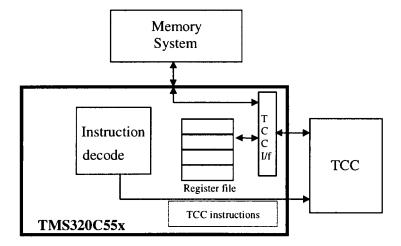

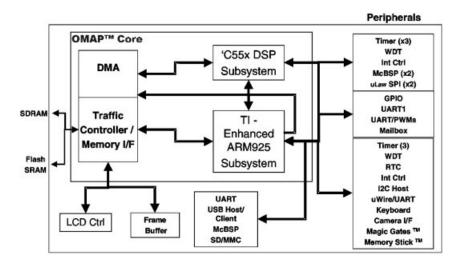

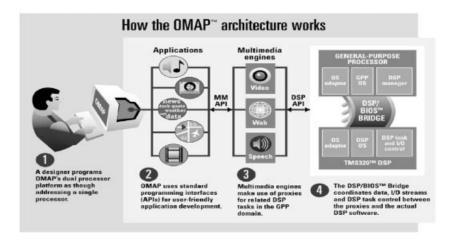

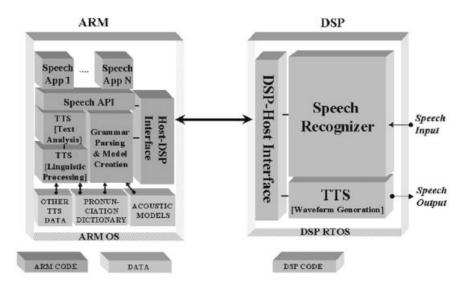

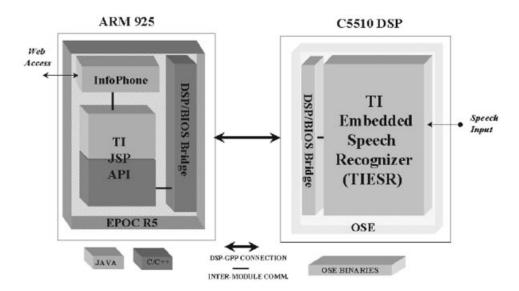

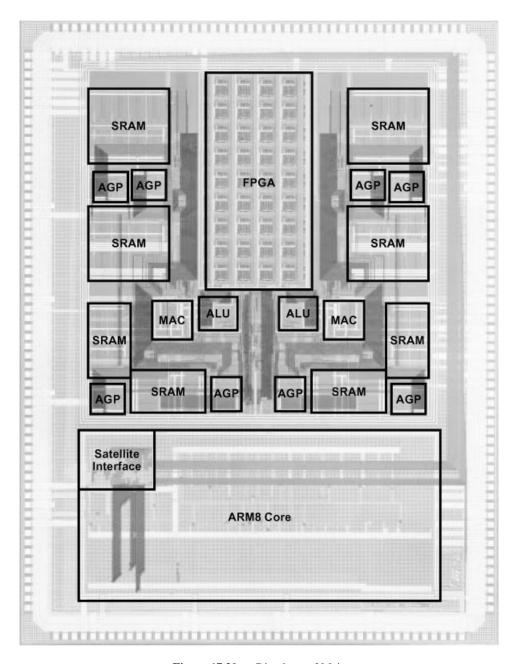

| 7.2 OMAP H/W Architecture                                                                           | 111        |  |

| 7.2.1 Architecture Description                                                                      | 111        |  |

| 7.2.2 Advantages of a Combined RISC/DSP Architecture                                                | 113        |  |

| 7.2.3 TMS320C55x and Multimedia Extensions                                                          | 113        |  |

| 7.3 OMAP S/W Architecture                                                                           | 114        |  |

| 7.4 OMAP Multimedia Applications                                                                    | 116        |  |

| 7.4.1 Video                                                                                         | 116        |  |

| 7.4.2 Speech Applications 7.5 Conclusion                                                            | 116<br>117 |  |

|                                                                                                     | 117        |  |

| Further Reading                                                                                     | 117        |  |

| 9 A Florible Distributed Jose Environment for Window DDA Architectures Dogod on DCD                 |            |  |

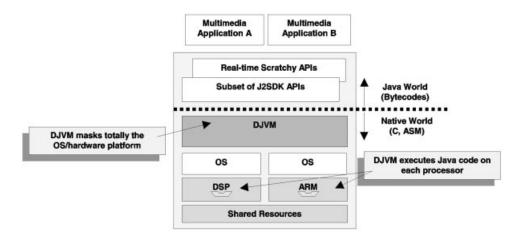

| 8 A Flexible Distributed Java Environment for Wireless PDA Architectures Based on DSP<br>Technology | 119        |  |

| Gilbert Cabillic, Jean-Philippe Lesot, Frédéric Parain, Michel Banâtre, Valérie Issarny, Teresa     | 11)        |  |

| Higuera, Gérard Chauvel, Serge Lasserre and Dominique D'Inverno                                     |            |  |

| 8.1 Introduction                                                                                    | 119        |  |

| 8.2 Java and Energy: Analyzing the Challenge                                                        | 120        |  |

| 8.2.1 Analysis of Java Opcodes                                                                      | 120        |  |

| 8.2.2 Analyzing Application Behavior                                                                | 121        |  |

| 8.2.3 Analysis                                                                                      | 125        |  |

| 8.3 A Modular Java Virtual Machine                                                                  | 127        |  |

| 8.3.1 Java Implantation Possibilities                                                               | 127        |  |

| 8.3.2 Approach: a Modular Java Environment                                                          | 129        |  |

| 8.3.3 Comparison with Existing Java Environments                                                    | 131        |  |

| 8.4 Ongoing Work on Scratchy                                                                        | 132        |  |

| 8.4.1 Multi-Application Management                                                                  | 133        |  |

| 8.4.2 Managing the Processor's Heterogeneity and Architecture                                       | 133        |  |

| 8.4.3 Distribution of Tasks and Management of Soft Real-Time Constraints                            | 133        |  |

| 8.4.4 Energy Management                                                                             | 133        |  |

| 8.5 Conclusion                                                                                      | 133        |  |

| References                                                                                          | 134        |  |

|                                                                                                     |            |  |

| 9 Speech Coding Standards in Mobile Communications                                                  | 137        |  |

| Erdal Paksoy, Vishu Viswanathan and Alan McCree                                                     |            |  |

| 9.1 Introduction                                                                                    | 137        |  |

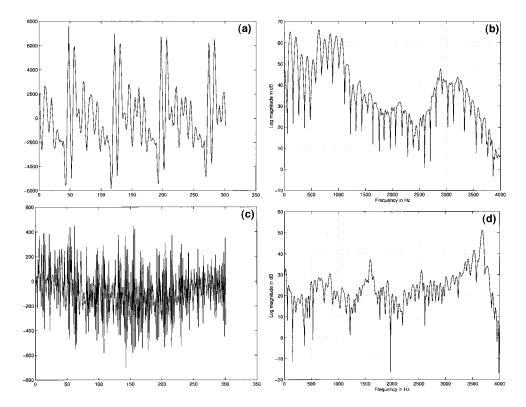

| 9.2 Speech Coder Attributes                                                                         | 138        |  |

| 9.3 Speech Coding Basics                                                                            | 139        |  |

| 9.3.1 Waveform Coders                                                                               | 141        |  |

| 9.3.2 Parametric Coders                                                                             | 141        |  |

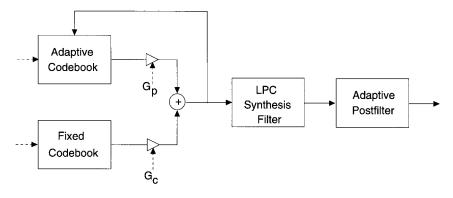

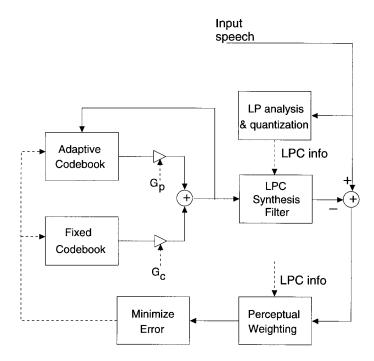

| 9.3.3 Linear Predictive Analysis-by-Synthesis                                                       | 143        |  |

| 9.3.4 Postfiltering                                                                                 | 146        |  |

| 9.3.5 VAD/DTX                                                                                       | 146        |  |

| 9.3.6 Channel Coding 9.4 Speech Coding Standards                                                    | 146        |  |

| 9.4.1 ITU-T Standards                                                                               | 147<br>147 |  |

| 9.4.2 Digital Cellular Standards                                                                    | 148        |  |

| 9.4.3 Wideband Standards                                                                            | 152        |  |

| 7. 1.5 Tracouna gianaaras                                                                           | 134        |  |

viii Contents

| 050 1011 42                                                                                          | 152 |

|------------------------------------------------------------------------------------------------------|-----|

| 9.5 Speech Coder Implementation                                                                      | 153 |

| 9.5.1 Specification and Conformance Testing                                                          | 153 |

| 9.5.2 ETSI/ITU Fixed-Point C                                                                         | 154 |

| 9.5.3 DSP Implementation                                                                             | 155 |

| 9.6 Conclusion                                                                                       | 155 |

| Acknowledgements                                                                                     | 156 |

| References                                                                                           | 156 |

| 10 Speech Recognition Solutions for Wireless Devices                                                 | 160 |

| Yeshwant Muthusamy, Yu-Hung Kao and Yifan Gong                                                       | 100 |

| 10.1 Introduction                                                                                    | 160 |

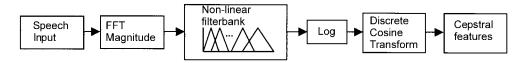

| 10.2 DSP Based Speech Recognition Technology                                                         | 160 |

| 10.2.1 Problem: Handling Dynamic Vocabulary                                                          | 161 |

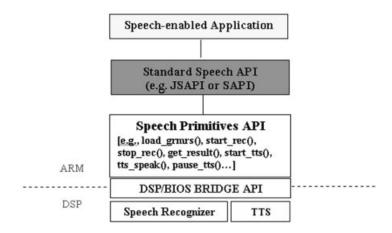

| 10.2.2 Solution: DSP-GPP Split                                                                       | 161 |

| 10.3 Overview of Texas Instruments DSP Based Speech Recognizers                                      | 161 |

| 10.3.1 Speech Recognition Algorithms Supported                                                       | 161 |

| 10.3.2 Speech Databases Used                                                                         | 161 |

| •                                                                                                    | 162 |

| 10.3.3 Speech Recognition Portfolio 10.4 TIESR Details                                               | 165 |

| 10.4.1 Distinctive Features                                                                          |     |

|                                                                                                      | 165 |

| 10.4.2 Grammar Parsing and Model Creation                                                            | 166 |

| 10.4.3 Fixed-Point Implementation Issues                                                             | 167 |

| 10.4.4 Software Design Issues                                                                        | 168 |

| 10.5 Speech-Enabled Wireless Application Prototypes                                                  | 168 |

| 10.5.1 Hierarchical Organization of APIs                                                             | 169 |

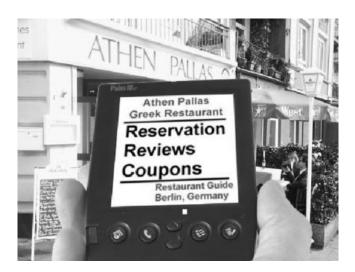

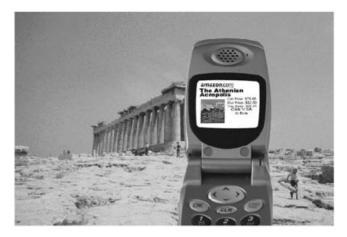

| 10.5.2 InfoPhone                                                                                     | 171 |

| 10.5.3 Voice E-mail                                                                                  | 172 |

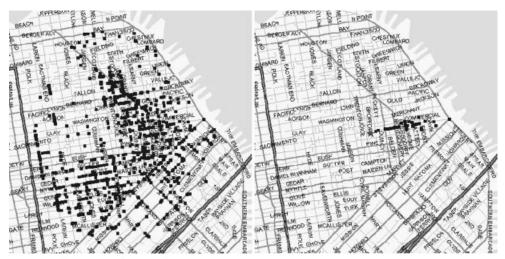

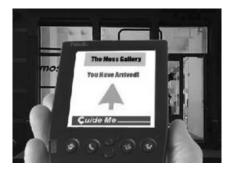

| 10.5.4 Voice Navigation                                                                              | 173 |

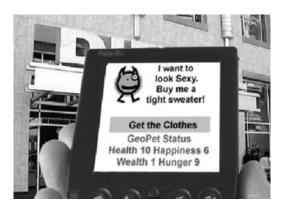

| 10.5.5 Voice-Enabled Web Browsing                                                                    | 174 |

| 10.6 Summary and Conclusions                                                                         | 175 |

| References                                                                                           | 176 |

| 11 Video and Audio Coding for Mobile Applications                                                    | 179 |

| Jennifer Webb and Chuck Lueck                                                                        |     |

| 11.1 Introduction                                                                                    | 179 |

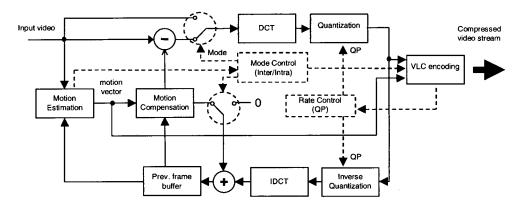

| 11.2 Video                                                                                           | 181 |

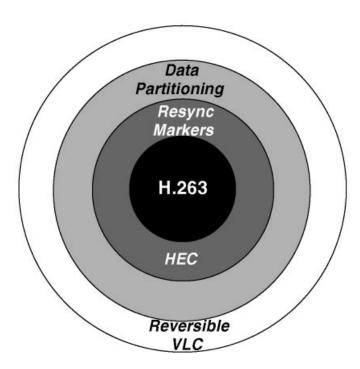

| 11.2.1 Video Coding Overview                                                                         | 182 |

| 11.2.2 Video Compression Standards                                                                   | 186 |

| 11.2.3 Video Coding on DSPs                                                                          | 187 |

| 11.2.4 Considerations for Mobile Applications                                                        | 188 |

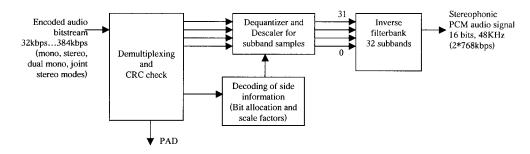

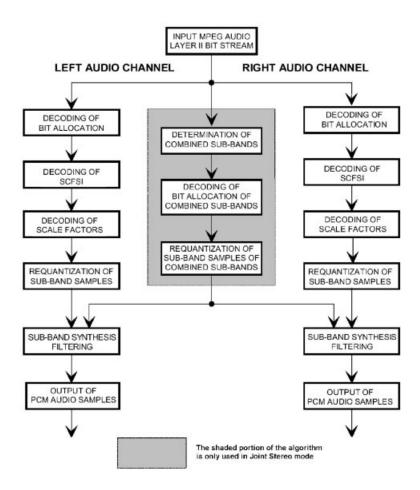

| 11.3 Audio                                                                                           | 190 |

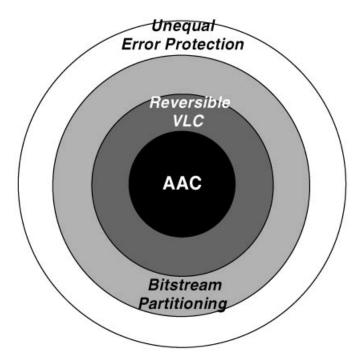

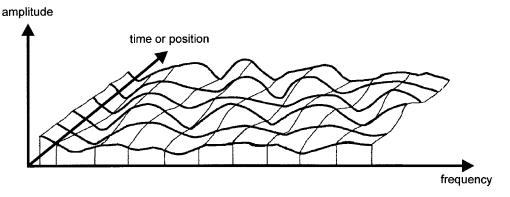

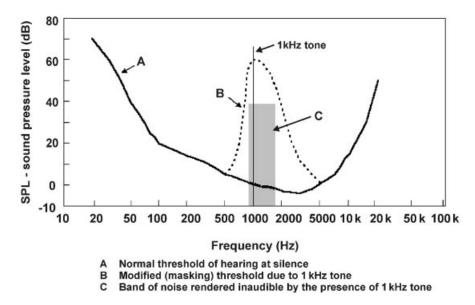

| 11.3.1 Audio Coding Overview                                                                         | 191 |

| 11.3.2 Audio Compression Standards                                                                   | 193 |

| 11.3.3 Audio Coding on DSPs                                                                          | 195 |

| 11.3.4 Considerations for Mobile Applications                                                        | 196 |

| 11.4 Audio and Video Decode on a DSP                                                                 | 198 |

| References                                                                                           | 200 |

| 12 Security Paradiam for Mahila Terminals                                                            | 201 |

| 12 Security Paradigm for Mobile Terminals  Edgar Auslandar Jaroma Azama Alain Chategy and Loic Hamon | 201 |

| Edgar Auslander, Jerome Azema, Alain Chateau and Loic Hamon 12.1 Mobile Commerce General Environment | 202 |

|                                                                                                      | 202 |

| 12.2 Secure Platform Definition                                                                      | 203 |

| 12.2.1 Security Paradigm Alternatives                                                                | 204 |

| 12.2.2 Secure Platform Software Component                                                            | 204 |

| 12.2.3 Secure Platform Hardware Component                                                            | 205 |

Contents ix

| 12.3 Software Based Security Component 12.3.1 Java and Security 12.3.2 Definition              | 205<br>205<br>205 |

|------------------------------------------------------------------------------------------------|-------------------|

| 12.3.3 Features for Security                                                                   | 206               |

| 12.3.4 Dependency on OS                                                                        | 207               |

| 12.4 Hardware Based Security Component: Distributed Security                                   | 207               |

| 12.4.1 Secure Mode Description                                                                 | 208               |

| 12.4.2 Key Management                                                                          | 210               |

| 12.4.3 Data Encryption and Hashing                                                             | 211               |

| 12.4.4 Distributed Security Architecture                                                       | 212               |

| 12.4.5 Tampering Protection                                                                    | 213               |

| 12.5 Secure Platform in Digital Base Band Controller/MODEM                                     | 214               |

| 12.6 Secure Platform in Application Platform                                                   | 215               |

| 12.7 Conclusion                                                                                | 215               |

| 13 Biometric Systems Applied To Mobile Communications                                          | 217               |

| Dale R. Setlak and Lorin Netsch                                                                | 215               |

| 13.1 Introduction                                                                              | 217               |

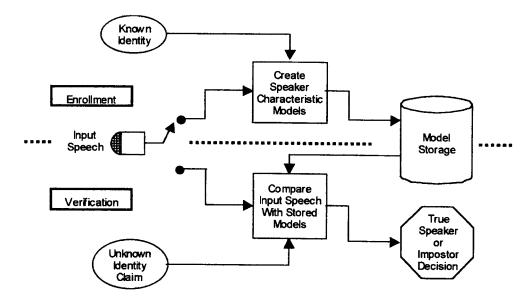

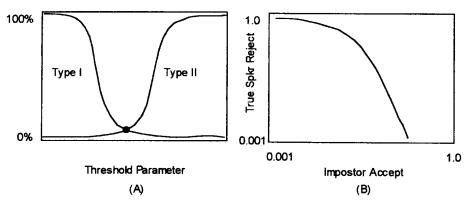

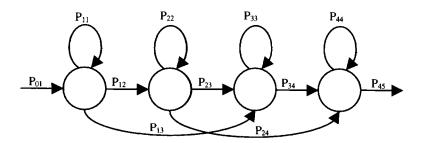

| 13.2 The Speaker Verification Task                                                             | 219               |

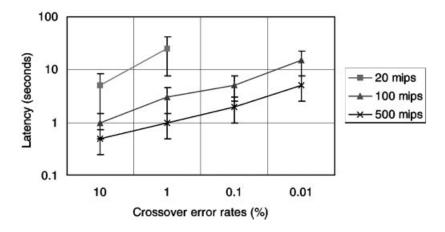

| 13.2.1 Speaker Verification Processing Overview 13.2.2 DSP-Based Embedded Speaker Verification | 219<br>224        |

| 13.3 Live Fingerprint Recognition Systems                                                      | 225               |

| 13.3.1 Overview                                                                                | 225               |

| 13.3.2 Mobile Application Characterization                                                     | 226               |

| 13.3.3 Concept of Operations                                                                   | 226               |

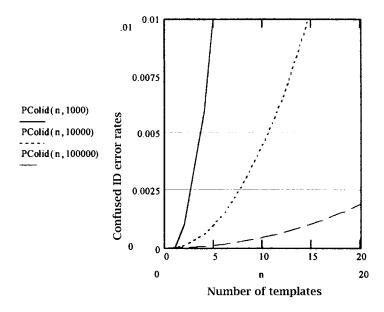

| 13.3.4 Critical Performance Metrics                                                            | 228               |

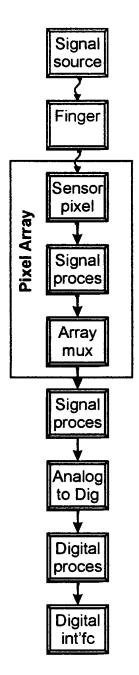

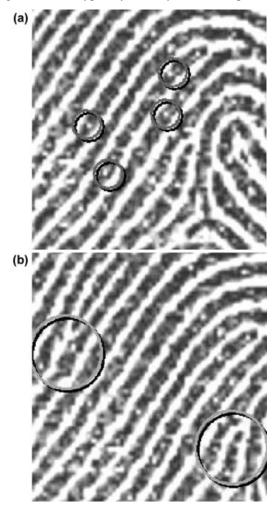

| 13.3.5 Basic Elements of the Fingerprint System                                                | 233               |

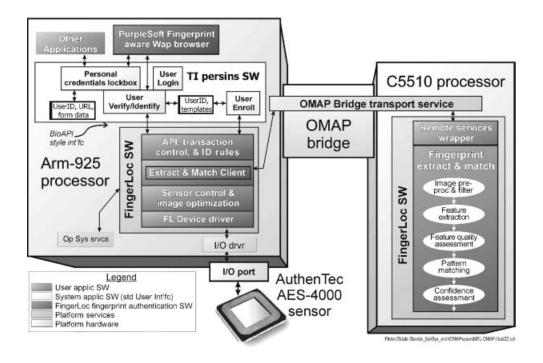

| 13.3.6 Prototype Implementation                                                                | 247               |

| 13.3.7 Prototype System Processing                                                             | 248               |

| 13.4 Conclusions                                                                               | 251               |

| References                                                                                     | 251               |

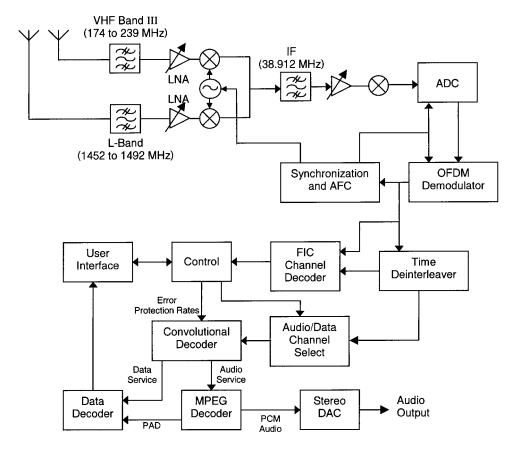

| 14 The Role of Programmable DSPs in Digital Radio                                              | 253               |

| Trudy Stetzler and Gavin Ferris                                                                |                   |

| 14.1 Introduction                                                                              | 253               |

| 14.2 Digital Transmission Methods                                                              | 254               |

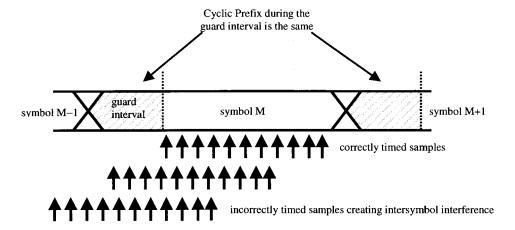

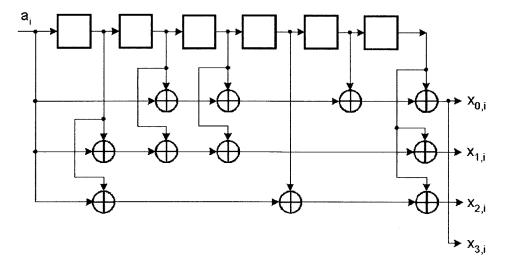

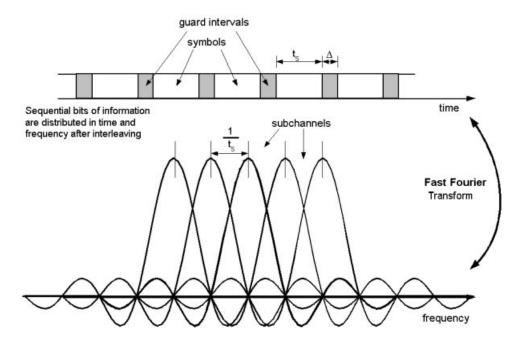

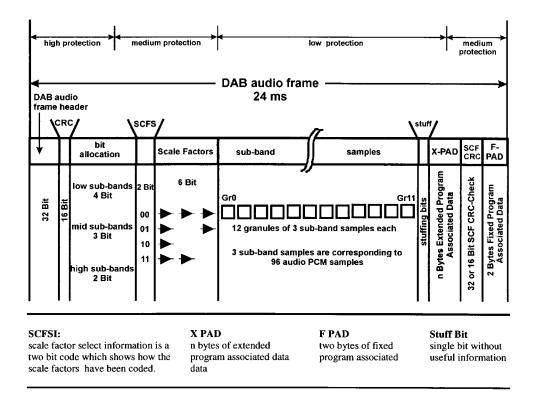

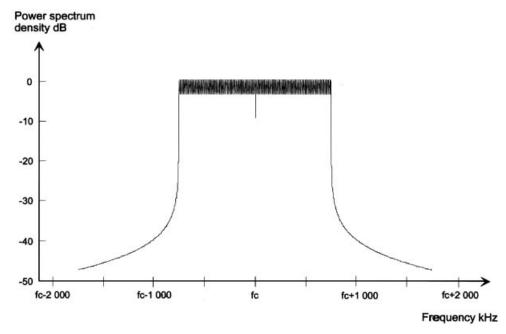

| 14.3 Eureka-147 System                                                                         | 255               |

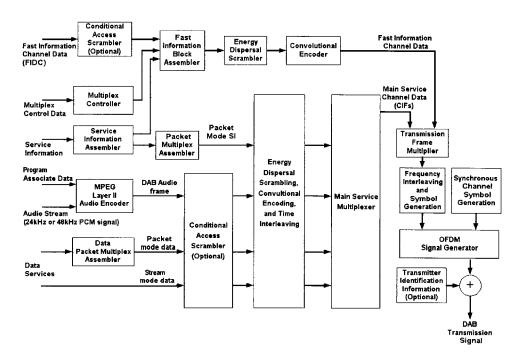

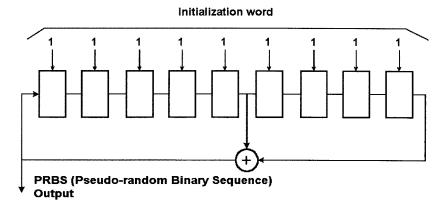

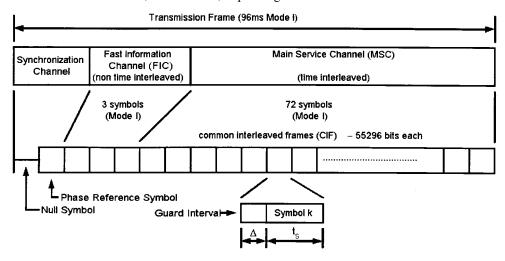

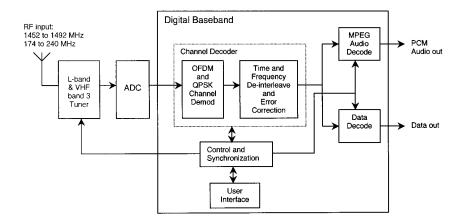

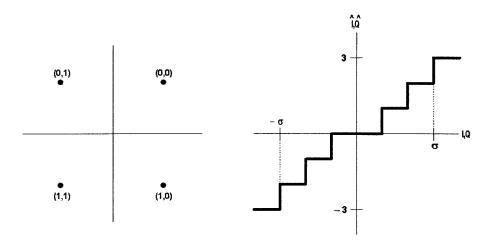

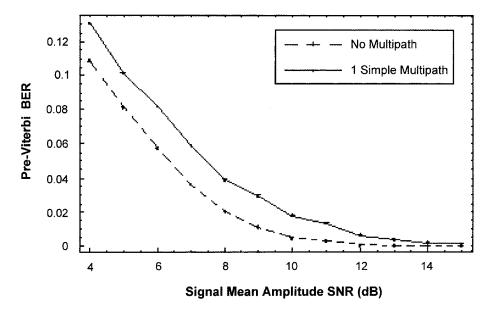

| 14.3.1 System Description                                                                      | 255<br>262        |

| 14.3.2 Transmission Signal Generation 14.3.3 Receiver Description                              | 265               |

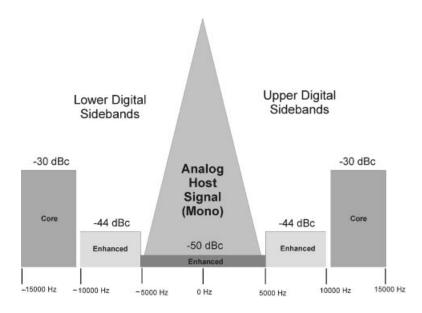

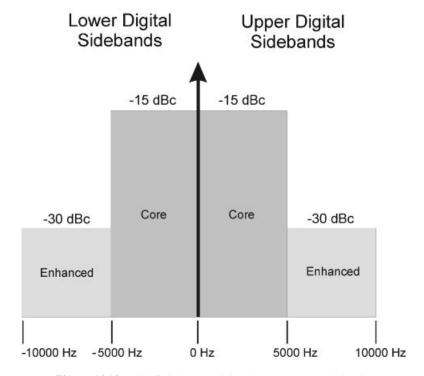

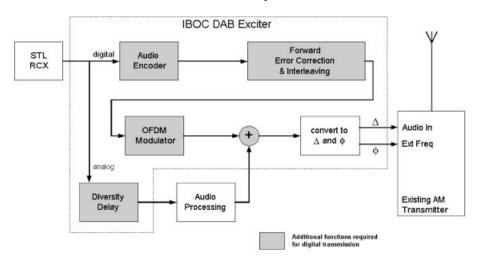

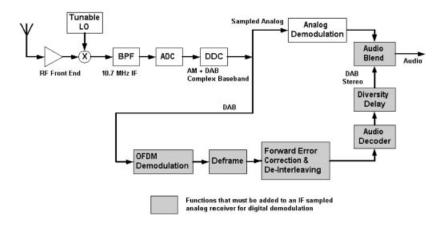

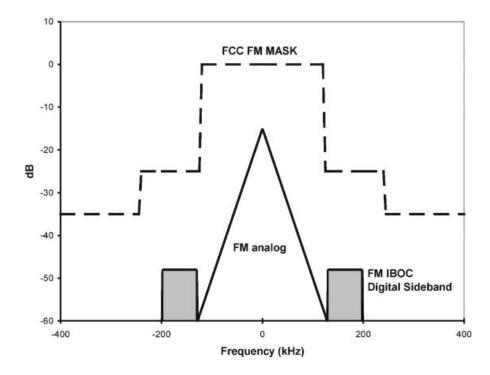

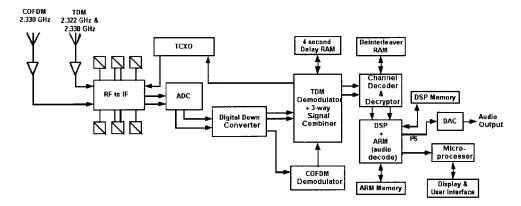

| 14.4 IBOC                                                                                      | 279               |

| 14.5 Satellite Systems                                                                         | 284               |

| 14.6 Conclusion                                                                                | 285               |

| References                                                                                     | 286               |

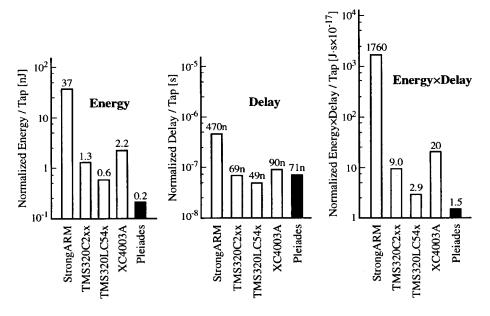

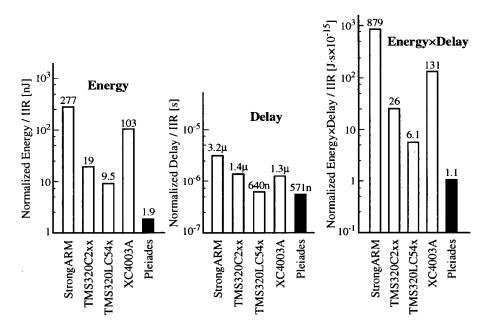

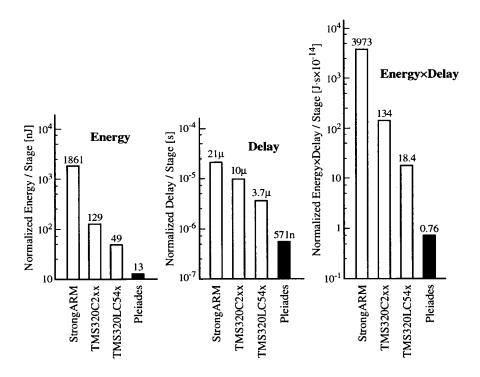

| 15 Benchmarking DSP Architectures for Low Power Applications                                   | 287               |

| David Hwang, Cimarron Mittelsteadt and Ingrid Verbauwhede                                      |                   |

| 15.1 Introduction                                                                              | 287               |

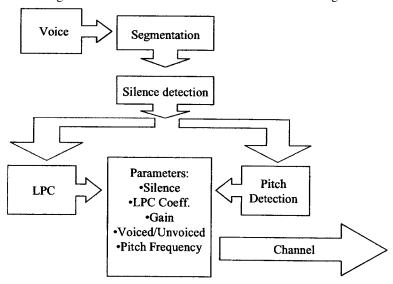

| 15.2 LPC Speech Codec Algorithm                                                                | 288               |

| 15.2.1 Segmentation                                                                            | 288               |

| 15.2.2 Silence Detection                                                                       | 288               |

| 15.2.3 Pitch Detection Algorithm                                                               | 289               |

| 15.2.4 LPC Analysis – Vocal Tract Modeling                                                     | 289               |

| 15.2.5 Bookkeeping                                                                             | 290               |

x Contents

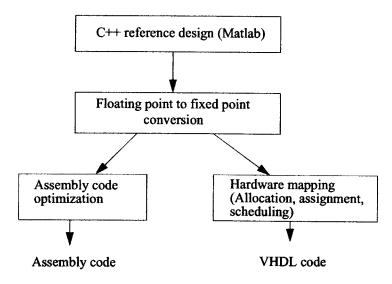

| 15.3 Design Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 290 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 15.3.1 Floating-Point to Fixed-Point Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 290 |

| 15.3.2 Division Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 292 |

| 15.3.3 Hardware Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 293 |

| 15.4 Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 293 |

| 15.4.1 Texas Instruments TI C54x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 293 |

| 15.4.2 Texas Instruments TI C55x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 294 |

| 15.4.3 Texas Instruments TI C6x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 294 |

| 15.4.4 Ocapi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 294 |

| 15.4.5 AIRT Designer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 294 |

| 15.5 Final Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 294 |

| 15.5.1 Area Estimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 295 |

| 15.5.2 Power Estimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 295 |

| 15.6 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 297 |

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 298 |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 298 |

| Note to the second secon | 270 |

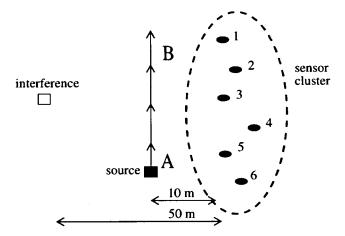

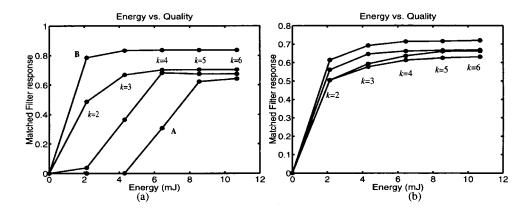

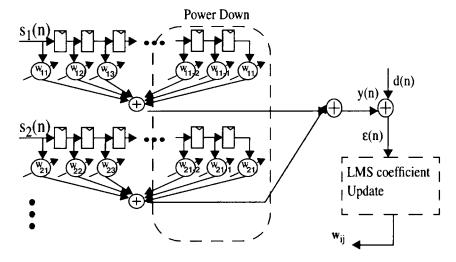

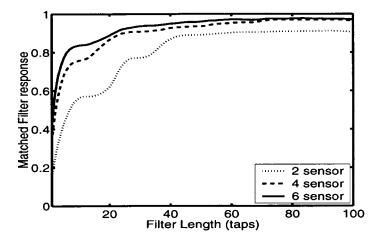

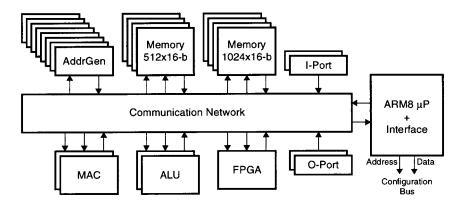

| 16 Low Power Sensor Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 299 |

| Alice Wang, Rex Min, Masayuki Miyazaki, Amit Sinha and Anantha Chandrakasan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

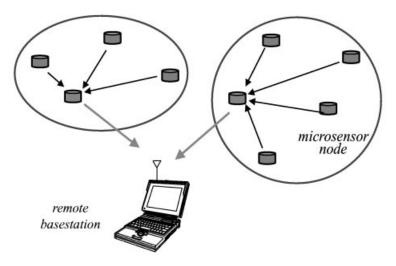

| 16.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 299 |

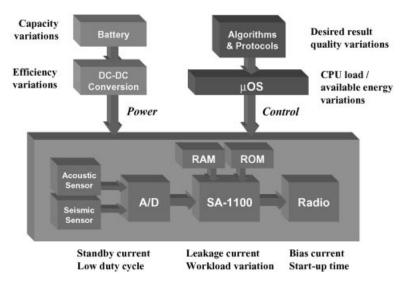

| 16.2 Power-Aware Node Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 300 |

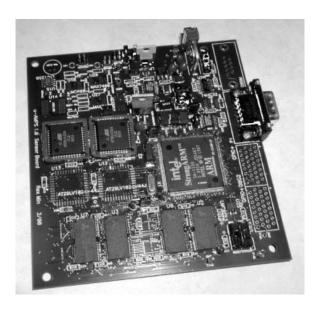

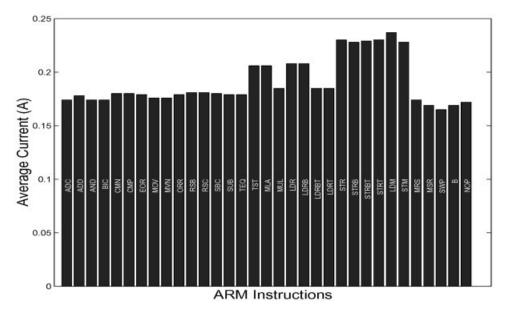

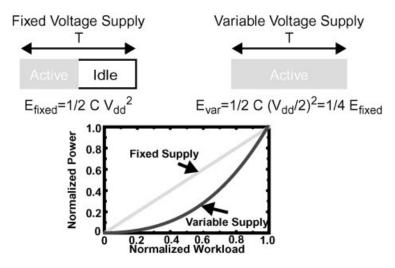

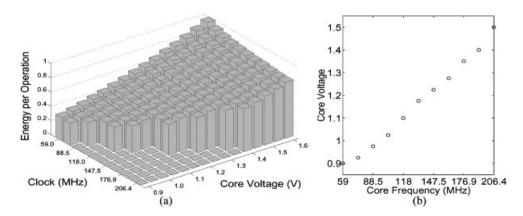

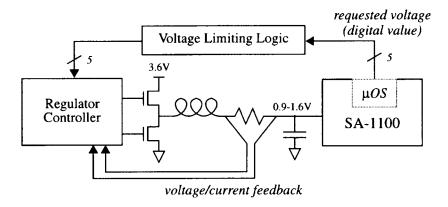

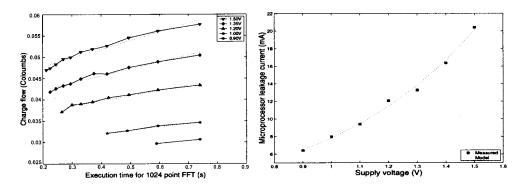

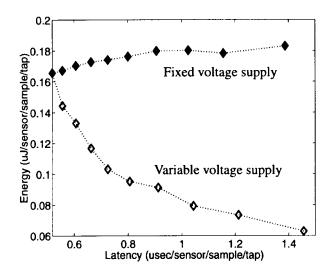

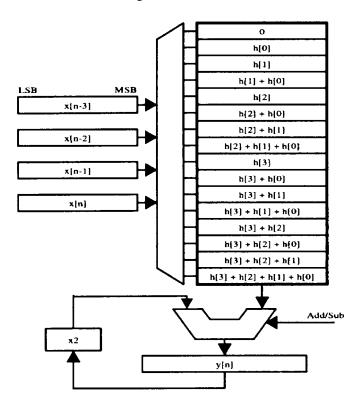

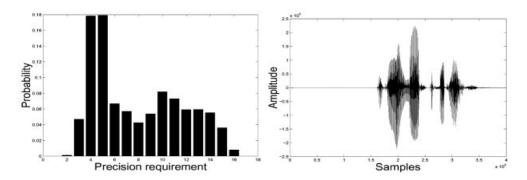

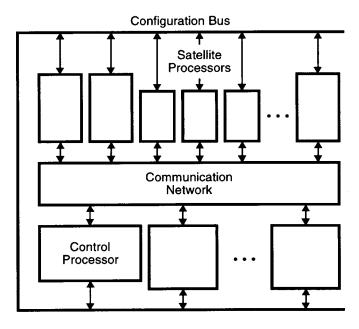

| 16.3 Hardware Design Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 302 |