# V.90 modem software on ADSP 218x family

# **User's Guide**

Version 5.3 February 6th, 1999

# TABLE OF CONTENTS

| 1. INTRODUCTION                                       | 5   |

|-------------------------------------------------------|-----|

| 1.1. PRODUCT OVERVIEW                                 | 5   |

| 1.1.1. Modulation core                                | 5   |

| 1.1.2. Protocol core                                  | 5   |

| 1.1.3. line drivers                                   |     |

| 1.1.4. data/control interfaces for data-pump software | 6   |

| 1.1.5. data/control interfaces for modem software     |     |

| 1.1.6. boot interface                                 |     |

| 1.2. PRODUCT FORMAT                                   |     |

| 1.2.1. source files                                   |     |

| 1.2.2. object files                                   |     |

| 1.2.3. executable/binary files                        |     |

| 1.3. MINIMUM PROCESSOR REQUIREMENTS                   |     |

| 1.4. MEMORY AND MIPS REQUIREMENTS                     |     |

| 1.5. DOCUMENT OVERVIEW                                |     |

| 1.6. RELATED DOCUMENTS                                |     |

| 2. BOOT INTERFACE                                     | 12  |

| 2.1. THROUGH BDMA PORT                                | 12  |

| 2.2. THROUGH IDMA FORT                                |     |

| 2.3. BOOT DURATION RESTRICTIONS                       |     |

| 2.4. FLOW DIAGRAM OF BOOT SEQUENCE                    |     |

|                                                       |     |

| 3. LINE DRIVERS                                       | .14 |

| 3.1. INTRODUCTION                                     | 14  |

| 3.2. CODEC INTERFACES                                 | 14  |

| 3.2.1. AD1843 codec                                   |     |

| 3.2.2. AD1819 codec                                   | 14  |

| 3.2.3. AD73311 codec                                  | 14  |

| 3.2.4. SGS-THOMSON STLC7545 codec                     | 14  |

| 3.3. T1 (E1) INTERFACE DEVICE                         | 14  |

| 4. HOST INTERFACE (MODEM SOFTWARE)                    | 15  |

|                                                       |     |

| 4.1. INTRODUCTION                                     |     |

| 4.1.1. modem block diagram                            |     |

| 4.1.2. data flow                                      |     |

| 4.1.3. control flow                                   |     |

| 4.1.3.1. The IDMA Interface                           |     |

| 4.1.3.3. modern setup                                 |     |

| 4.2. DATA INTERFACE                                   |     |

| 4.2.1. Introduction                                   | -   |

| 4.2.2. The SCC structure                              |     |

| 4.2.3. UART SCC                                       |     |

| 4.2.3.1. SCC structure                                |     |

| 4.2.3.2. UART receive BufferDescriptor (RXbd)         |     |

| 4.2.3.3. UART transmit BufferDescriptor (TX bd)       |     |

| 4.2.3.4. IDMA - SCC2 receiver interaction             |     |

| 4.2.3.5. IDMA - SCC2 transmitter interaction          |     |

| 4.2.4. Asynchronous HDLC SCC                          |     |

| 4.2.4.1. The SCC structure                            |     |

| 4.2.4.3. async HDLC transmit BufferDescriptor (TX bd) |     |

| 4.2.4.4. IDMA - SCC3 transmitter interaction          |     |

| 4.2.4.5. IDMA- SCC3 receiver interaction              | 45  |

| 4.3. CONTROL INTERFACE                                | 47  |

| 4.3.1. AT set control interface                       | 47  |

| 4.3.1.1. Command Language Syntax                      |     |

| 4.3.1.2. General at_set commands                      |     |

| 4.3.1.3. S-Registers                                  |     |

| 4.3.1.4. %S Registers                           |     |

|-------------------------------------------------|-----|

| 4.3.2. IDMA control interface                   |     |

| 4.4. IDMA MODEM SCRIPTS                         |     |

| 4.4.1. Power up sequence                        |     |

| 4.4.2. modem connect sequence                   |     |

| 4.4.3. modem disconnect sequence                |     |

| 4.4.4. Statistics                               |     |

| 4.5. MODEM EVENT CODES                          |     |

| 5. HOST INTERFACE (DATA-PUMP SOFTWARE)          |     |

| 5.1. INTRODUCTION                               |     |

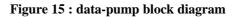

| 5.1.1. data-pump block diagram                  |     |

| 5.1.2. data flow                                |     |

| 5.1.2. data flow<br>5.1.3. control flow         |     |

| 5.1.3.1. The IDMA interface                     |     |

| 5.1.3.1. The IDMA Interface                     |     |

| 5.1.3.3. data-pump Status                       |     |

| 5.2. DATA INTERFACE                             |     |

| 5.2.1. parallel synchronous interface           |     |

| 5.2.2. Synchronous HDLC SCC                     |     |

| 5.2.2.1. The SCC Structure                      |     |

| 5.2.2.2. HDLC receive BufferDescriptor (RX bd)  |     |

| 5.2.2.3. HDLC transmit BufferDescriptor (TX bd) |     |

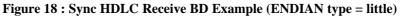

| 5.2.2.4. IDMA - SCC1 transmitter interaction    |     |

| 5.2.2.5. IDMA- SCC1 receiver interaction        |     |

| 5.2.3. Uart SCC                                 |     |

| 5.2.3.1. The SCC Structure                      |     |

| 5.2.3.2. UART receive BufferDescriptor (RX bd)  |     |

| 5.2.3.3. UART transmit BufferDescriptor (TX bd) |     |

| 5.2.3.4. IDMA - SCC1 transmitter interaction    |     |

| 5.2.3.5. IDMA- SCC1 receiver interaction        |     |

| 5.3. CONTROL INTERFACE                          |     |

| 5.3.1. data-pump write database                 |     |

| 5.3.2. data-pump read database                  |     |

| 5.4. IDMA DATA-PUMP SCRIPTS                     |     |

| 5.4.1. IDMA control sequences                   |     |

| 5.4.2. data-pump supervisory rules              |     |

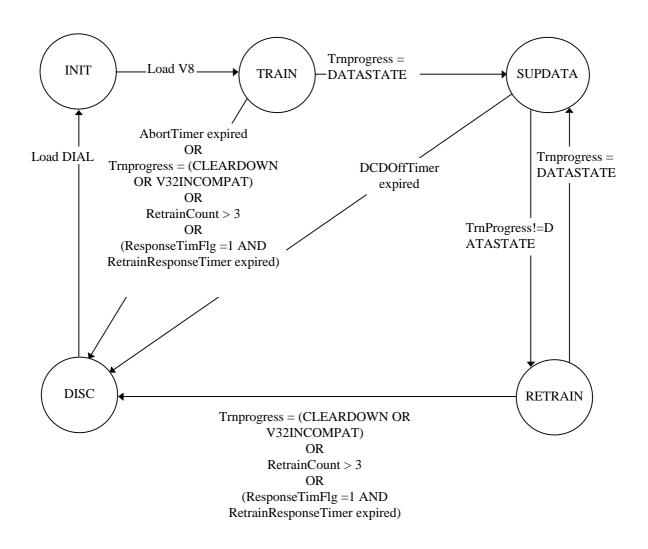

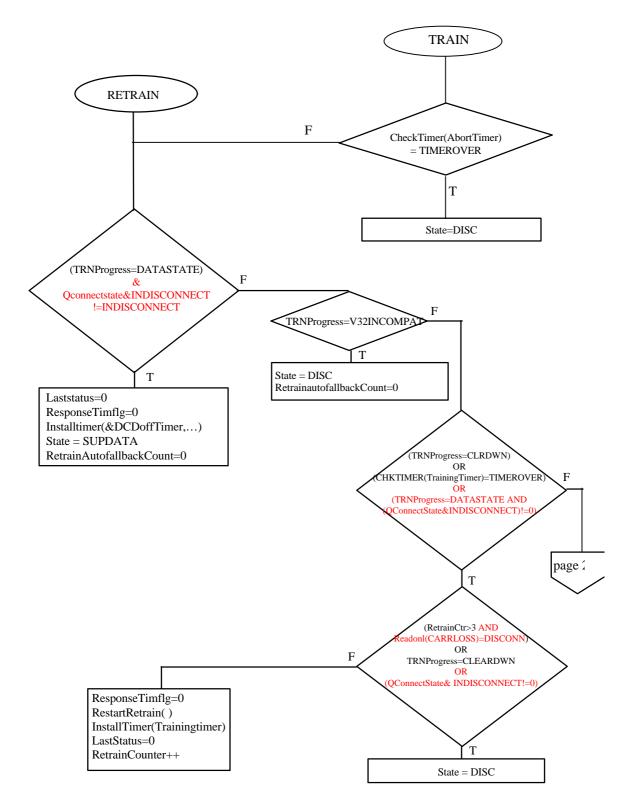

| 5.4.2.1. data-pump supervisor state diagram     |     |

| 5.4.2.2. data-pump line-follow-up flow diagram  |     |

| 5.5. DATA-PUMP EVENT CODES                      |     |

| 6. APPENDIX                                     |     |

| 6.1. FILE FORMAT FOR IDMA BOOTING               | 142 |

| 6.1.1. header table                             |     |

| 6.1.2. body table                               |     |

| 6.2. FILE FORMAT FOR BDMA BOOTING               |     |

| 6.3. EVENT INTERFACE REGISTERS                  |     |

| 6.4. MODEM INTERFACE LOCATIONS                  |     |

|                                                 |     |

| 6.5. DATA-PUMP INTERFACE LOCATIONS              |     |

| 6.6. EYE PATTERN DISPLAY                        |     |

| 6.6.1. V.32.                                    |     |

| 6.6.2. V.34.                                    |     |

| 6.7. TRAINING STATE DIAGRAMS                    |     |

| 6.8. SNR TABLE                                  |     |

| 6.9. OVERVIEW MODEM STANDARDS                   |     |

# TABLE OF FIGURES

| Figure 1 : System block diagram                                                           | 5 |

|-------------------------------------------------------------------------------------------|---|

| Figure 2 : boot operation flow diagram                                                    |   |

| Figure 3 : line interface                                                                 |   |

| Figure 4 : modem block diagram                                                            |   |

| Figure 5 : UART Receive BufferDescriptor                                                  |   |

| Figure 6 : UART RX BD Example                                                             |   |

| Figure 7 : UART Transmit BufferDescriptor                                                 |   |

| Figure 8 : flow diagram of interaction between SCC2 receiver and the IDMA host            |   |

| Figure 9 : flow diagram of interaction between SCC2 transmitter and the IDMA host         |   |

| Figure 10 : Async HDLC Receive BD Example (little endian)                                 |   |

| Figure 11: ASYNC HDLC Transmit BufferDescriptor                                           |   |

| Figure 12 : Async HDLC Transmit BD Example (little endian)                                |   |

| Figure 13 : IDMA - SCC3 transmitter interaction (little endian)                           |   |

| Figure 14 : IDMA - SCC3 receiver interaction (little endian)                              |   |

| Figure 15 : data-pump block diagram                                                       |   |

| Figure 16 : databuffers of the parallel synchronous interface                             |   |

| Figure 17 : HDLC Receive BufferDescriptor                                                 |   |

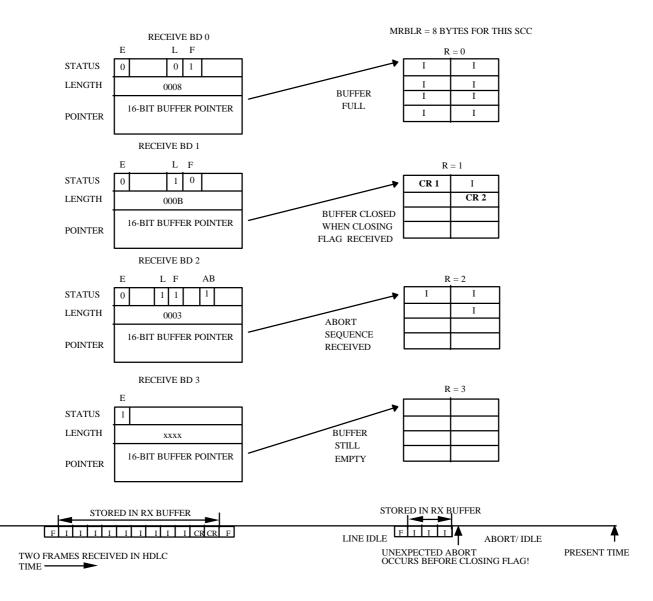

| Figure 18 : Sync HDLC Receive BD Example (ENDIAN type = little)                           |   |

| Figure 19 : HDLC Transmit BufferDescriptor                                                |   |

| Figure 20 : IDMA - SCC1 transmitter interaction for synchronous HDLC mode (little Endian) |   |

| Figure 21 : IDMA- SCC1 receiver interaction for synchronous HDLC mode (little Endian)     |   |

| Figure 22 : character format of the UART                                                  |   |

| Figure 23 : UART Receive BufferDescriptor                                                 |   |

| Figure 24 : UART Receive BD Example (little Endian)                                       |   |

| Figure 25 : UART Transmit BufferDescriptor                                                |   |

| Figure 26 : IDMA - SCC1 transmitter interaction (little Endian)                           |   |

| Figure 27 : IDMA - SCC1 receiver interaction (little Endian)                              |   |

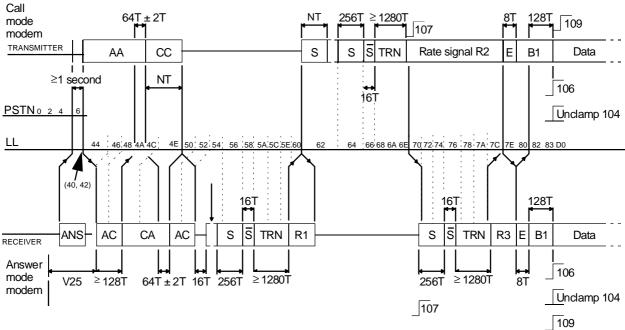

| Figure 28: supervisor state diagram                                                       |   |

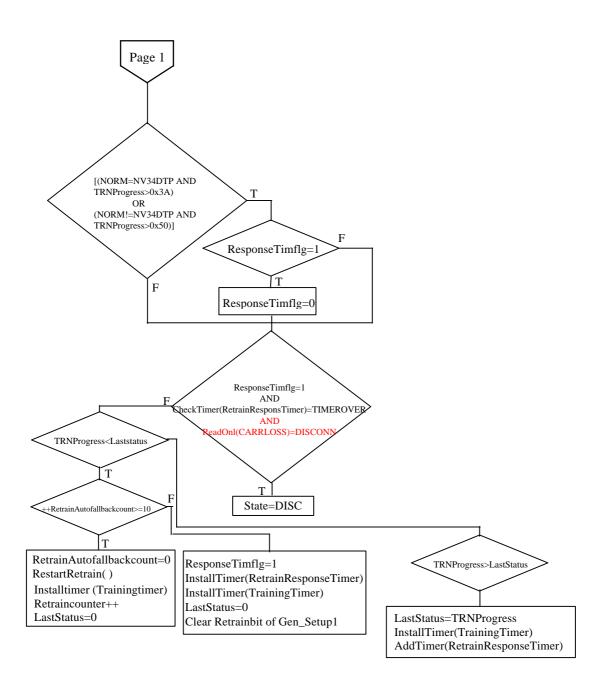

| Figure 29: line follow up flow diagram for train and retrain state                        |   |

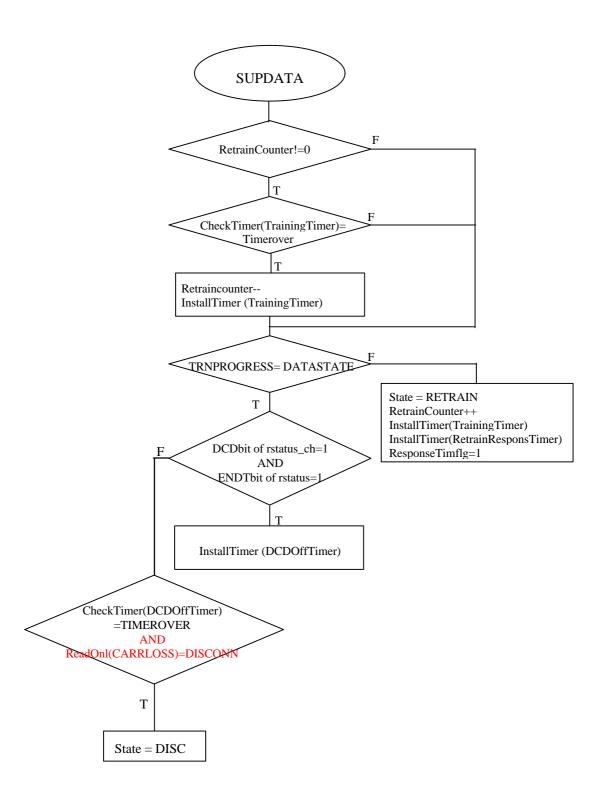

| Figure 30: line follow up flow diagram for supdata                                        |   |

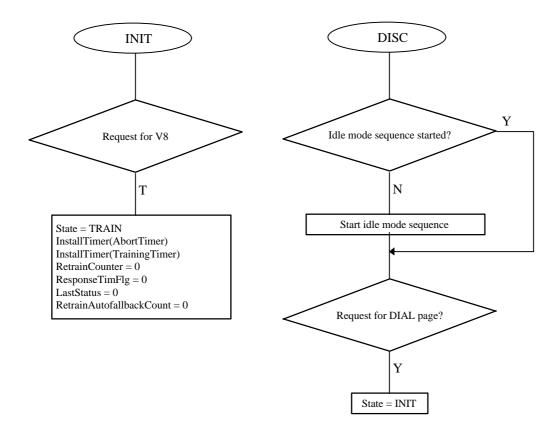

| Figure 31: line follow up flow diagram for INIT and DISC states                           |   |

# 1. INTRODUCTION

# **<u>1.1. PRODUCT OVERVIEW</u>**

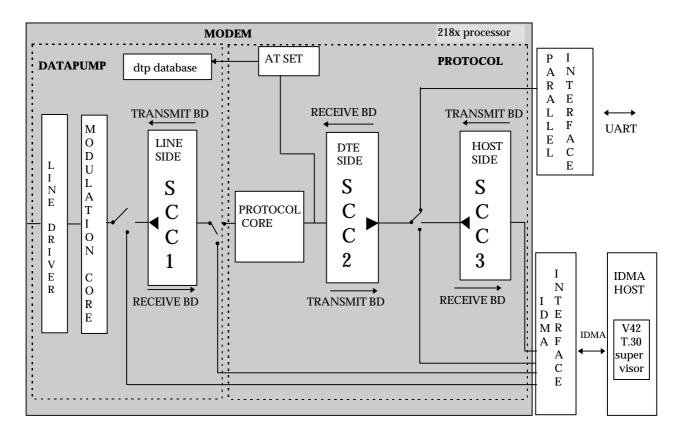

The Block diagram in Figure 1 gives an overview of the main building blocks (**modules**) in the system and their interconnection.

Figure 1 : System block diagram<sup>1</sup>

The DSP part of the software contains 2 **core modules**:

## 1.1.1. Modulation core

- Modulation complying with ITU-T V.90, V.34bis, V.34, V.32bis, V.32, V.22bis, V.22, V.23, V.21, Bell Recommendations Bell 212A, Bell 103.

- FAX mode modulation complying with V.17, V.27 ter, V.29, V.21 ch 2

- Country specific automatic dialler

## 1.1.2. Protocol core

- Error correction according to ITU-T V.42 or MNP 4 and data compression according to ITU-T V.42bis or MNP 5

- AT ® commands

- FAX class1, class2, T.30 protocol<sup>2</sup>

<sup>2</sup> In development

<sup>&</sup>lt;sup>1</sup> SCC = Serial Communications Controller; BD = Buffer Descriptor

In this document a software package *with protocol and modulation part* will be called '**modem**', a package *without protocol part* will be called '**data-pump**'.

The DSP software also contains several **peripheral modules**. For each of these peripherals a number of configurations exist.

## 1.1.3. line drivers

- AD1843 codec (daisy chain master and slave)

- AD1819 codec

- AD73311 codec

- SGS-Thomson STLC7545 codec

- T1\_E1 interface device

## 1.1.4. data/control interfaces for data-pump software

- idma synchronous data interface without framing

- idma data interface with asynchronous (V.14) framing through SCC1

- idma data interface with synchronous (HDLC) framing through SCC1

- idma memory mapped control interface via the data-pump database

## 1.1.5. data/control interfaces for modem software<sup>3</sup>

- idma asynchronous data interface with protocol through SCC2

- idma asynchronous data interface with protocol and HDLC framing through SCC3

- idma asynchronous control interface via AT SET commands

## 1.1.6. boot interface

- BDMA interface

- IDMA interface

The global software package also contains a number of modules running on the Host system, the **host modules**. These modules are written in C-language.

- V42 error correction<sup>4</sup> : in case of data-pump DSP systems that require a error free connection.

- T30 fax protocol : for fax class1 modem systems.

- data-pump supervisor : for control and follow up of the data-pump train and retrain behaviour.

$<sup>^{3}</sup>$  As shown in the block diagram a software configuration with an asynchronous data/control interface through a external UART component (16550) also is available. This configuration runs on a **demo-board.** A product which is at any time available for customer evaluation.

<sup>&</sup>lt;sup>4</sup> The V42 protocol as a host based module is currently in development

## **<u>1.2.</u> PRODUCT FORMAT**

The software package is available in several format types,

#### 1.2.1. source files

Following items currently are available in source code :

- Source code files for the all codec drivers. They can be used as a development starting point for customers having a very specific line driver solution.

- Certain parts of the protocol core, for those applications for which the data-pump software runs on the DSP and the protocol runs on the IDMA host system.

- Certain parts of the DSP kernel that could be useful as example to build you own kernel system.

- The BDMA loader software that follows the Telindus BDMA/IDMA binary file format.

- Certain utilities are available in source form, for example the prom split program that transforms the executable files into a binary file.

#### 1.2.2. object files

Some of the core and peripheral **modules** of the software are available in object file format. They are standalone linkable modules with a completely memory mapped interface. The object files specifically are of interest for **integrators**<sup>5</sup> who want to integrate these modules into their existing system. The object code is re-locatable. Following items currently are available in object format :

- modulation core modules for all modulations

- the SCC1 module for both V14 and HDLC framing

- line driver modules for all supported codec types.

## 1.2.3. executable/binary files

For both **data-pump** and **modem** software, we build and maintain **customised software** versions for specific user configurations<sup>6</sup>. These customised software versions are available for the **user** as a binary prom image file, for both IDMA and BDMA loading, or as executable (non re-locatable )code files. The latter case can be of interest for the **user** who prefers to start from a working modem or data-pump system, compiled for his platform, but wants to customise<sup>7</sup> this system :

- add specific tasks to the modem or data-pump task switcher tables at the executable level.

- tune the modem or data-pump by changing parameters in the set-up tables.

<u>IMPORTANT REMARK</u>: This document is intended for the **user** of the executable/binary format. It explains all aspects of the modem/data-pump interfacing through the IDMA port.

<sup>&</sup>lt;sup>5</sup> A related document, called *Integrator's Manual*, explains the integration of the object files.

<sup>&</sup>lt;sup>6</sup> A related document, called *Questionnaire*, should be used as a guide line to describe your software configuration. It's tables list all the configuration parameters together with their possible values. You should fill in the column 'customer'. It will allow us to compile customised software for you.

<sup>&</sup>lt;sup>7</sup> A related document, called *Integrator's Manual*, explains the integration of the executable files.

# **<u>1.3.</u> <u>MINIMUM PROCESSOR REQUIREMENTS</u>**

full featured modem software runs on :

- ADSP2187 (40Mips, only internal memory)

- ADSP2181 (40Mips, 3 external rams 32k\*8, 10 nsec access)

data-pump and fax class1 modem software run on :

• ADSP2181 (33Mips, only internal memory)

## data-pump software without SCC1, all modulations up to V.32bis runs on :

• ADSP2186 (33Mips, only internal memory)

# **<u>1.4. MEMORY AND MIPS REQUIREMENTS</u>**

The complete software is too large to fit into the DSP internal memory. Therefore, the software has been segmented into **bootpages**. Each page has a specific functionality.

Table 1: overview of bootpages, gives a brief functional description of all the pages. It lists the prom image file size and MIPS consumption for every page and also indicates the **bootpage number** for every page. All numbers are based on the RCS version TUPLE1 of June/98 and can slightly change during product development.

| page<br>nbr | Name                       | Functionality                                                                                                                                                                                                            | MIPS <sup>8</sup>  | prom image<br>file size (bytes) |

|-------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------|

| 9           | STARTUP                    | Loaded in memory <b>after reset</b> . It sets up the modem in a default state and provokes the loading of the dial page.                                                                                                 |                    |                                 |

| 0           | Dial                       | provides:<br>-ring detection (incoming calls)<br>-tone generation (DTMF, single tone)<br>-Country specific automatic dialler<br>These items are explained in detail in a related document, called<br>' <i>Dialler</i> '. | 3                  | 19752                           |

| 1           | V.22                       | covers ITU-T V.22, V.22bis, Bell B212A and modulation auto mode (EIA/TIA PN-2330)                                                                                                                                        | 6                  | 21999                           |

| 2           | V.32                       | covers ITU-T V.32, V.32bis and V.33                                                                                                                                                                                      | 12                 | 36964                           |

| 3           | fsk                        | covers ITU-T V.23, V.21, V.21 ch 2, and Bell 103                                                                                                                                                                         | 3                  | 12036                           |

| 4           | fax                        | covers ITU-T V.17, V.29, V.27ter                                                                                                                                                                                         | 7                  | 31872                           |

| 6           | V.8                        | cover ITU-T V.8                                                                                                                                                                                                          | 3                  | 23368                           |

| 7           | INFO                       | cover ITU-T V.34 and V.90 phase 2                                                                                                                                                                                        | 6                  | 22292                           |

| 8           | V.34                       | cover ITU-T V.34, phase 3-4                                                                                                                                                                                              | 24-30 <sup>9</sup> | 53002                           |

| 10          | modem protocol             | covers ITU-T v42, MNP4, ITU-T v42bis, MNP5, ODP/ADP, ASYNC PPP                                                                                                                                                           | 8 <sup>10</sup>    | 73660                           |

| 11          | AT ®-set off line          |                                                                                                                                                                                                                          | 1                  | 41200                           |

| 12          | AT ® -set on line          | covers TIES protocol                                                                                                                                                                                                     | 1                  | 8268                            |

| 13          | V.90A <sup>11</sup>        | cover ITU-T V.90, phase 3-4, APCM                                                                                                                                                                                        |                    |                                 |

| 14          | V.90D                      | cover ITU-T V.90, phase 3-4, DPCM                                                                                                                                                                                        | 2528 <sup>12</sup> | 51584                           |

| 15          | fax protocol <sup>13</sup> | covers ITU-T T.30                                                                                                                                                                                                        |                    |                                 |

| 16          | LL page                    | The 'low level' page provides a number of low level functions. They are explained in detail in a related document, called ' <i>Low level functions</i> '.                                                                |                    |                                 |

Table 1: overview of bootpages

<sup>&</sup>lt;sup>8</sup> For all modulation pages the MIPS have been measured for a data-pump without SCC1, to calculate the MIPS consumed by SCC1 following rule can be applied : **MIPS=(1/10000)\*linebitrate**

<sup>&</sup>lt;sup>9</sup> The MIPS consumption depends on the enabled features.

<sup>&</sup>lt;sup>10</sup> Assuming a DTE bit rate of 115200bps, 2K dictionary and 33600bps on line.

<sup>&</sup>lt;sup>11</sup> In development

<sup>&</sup>lt;sup>12</sup> The MIPS consumption depends on the enabled features

<sup>&</sup>lt;sup>13</sup> In development

Table 2: DM and PM of the object code modules, lists all currently available object code modules with their program and data memory size. All numbers are based on the RCS version TUPLE1 of June/98 and can slightly change during product development.

| Object code module                                           | PM size (words) | DM size (words) |  |

|--------------------------------------------------------------|-----------------|-----------------|--|

|                                                              | (words)         | (words)         |  |

| DIAL modulation core(tonedetection, generation, autodialler) | 4633            | 1426            |  |

| V.8 modulation core                                          | 2389            | 1912            |  |

| INFO modulation core                                         | 5072            | 5636            |  |

| v.90D modulation core                                        | 11000           | 9290            |  |

| V.34 modulation core                                         | 12978           | 9660            |  |

| V.32 modulation core(V.32,V.32bis,V33)                       | 7513            | 6476            |  |

| V.22 modulation core (V.22,V.22bis,automode)                 | 5699            | 1619            |  |

| FAX modulation core (V29,V27ter,V17)                         | 6705            | 6054            |  |

| FSK modulation core (V21,V23)                                | 2536            | 1487            |  |

| linedriver                                                   | 512             | 652             |  |

| SCC1(HDLC + V14)                                             | 4718            | 772             |  |

|                                                              |                 |                 |  |

Table 2: DM and PM of the object code modules

## **1.5. DOCUMENT OVERVIEW**

This document is organised as follows.

- Chapter 2 'BOOT INTERFACE', describes the process of loading software in internal memory.

- Chapter 3 'LINE DRIVERS' describes the analogue interface or line interface.

These Chapters are common for data-pump and modem software.

- Chapter 4 'HOST INTERFACE (MODEM SOFTWARE)' describes the interfacing between the HOST processor and DSP for the modem software

- Chapter 5 'HOST INTERFACE (DATA-PUMP SOFTWARE)' describes the interfacing between the HOST processor and DSP for the data-pump software.

General Remark:

Throughout this document, a data memory location in the DSP is never indicated by it's absolute address, but by a **symbolic name**. The same applies for a bit position within a location.

## **1.6. RELATED DOCUMENTS**

- 'INTEGRATORS MANUAL': this document discusses in detailed the topic of object code and executable code integration.

- 'LOW LEVEL FUNCTIONS' : gives a detailed description of the interface of all low level functions on the LL page.

- 'DIALLER' : gives a detailed description of interface and functionality of the low level dialler functions and of the automatic dialler present on the dial page.

- 'QUESTIONNAIRE' : should be used as a guide line to describe your software configuration. It's tables list all the configuration parameters together with their possible values. It will allow us to compile customised software for you.

# 2. BOOT INTERFACE

# 2.1. THROUGH BDMA PORT

An external ROM of at least 4 Mb is required to store the software, and should be connected to the BDMA port<sup>14</sup>. Loading is completely controller less:

- \* After reset the DSP will automatically load the STARTUP page and start execution.

- \* **During runtime** the DSP loads another page when necessary.

## 2.2. THROUGH IDMA PORT

The HOST processor loads the software using writes through the IDMA port<sup>15</sup> :

- After reset the STARTUP page should be loaded. DSP execution starts automatically after completing the download.

- During runtime a page should be loaded when requested by the DSP. This is discussed more in detail:

- DSP requests a page by pushing the corresponding event in the event buffer, sets the 'BOOT' bit in RSTATUS\_DBS, and puts itself in a wait state. The requested page is specified in location BOOTPAGE\_NR. Table 1: overview of bootpages, gives for each possible page the corresponding number.

- 2. HOST processor retrieves<sup>16</sup> the requested page from it's memory and starts loading it in the DSP 's memory.

- 3. After completing the download, HOST processor sets the **BOOTFINISHEDBIT** in location **WSTATUS**.

- 4. DSP starts execution of the new page.

## 2.3. BOOT DURATION RESTRICTIONS

The duration of the boot operation is restricted. The boot operations of the software happen at moments no activity is happening on the telephone line. These idle periods are restricted and so also is the boot period. Following rules apply:

- in general the idle period ( and boot operation) should never be longer than 75 ms

- when booting from INFO to V.34 idle time is restricted to 70 ms

- when booting from V.22 to V.32 idle time is restricted to 6.6 ms

- booting from Dial page can be done without any time restrictions

- retrain booting from V.34 to INFO is restricted by the retrain time out<sup>17</sup> of the remote modem.

<sup>&</sup>lt;sup>14</sup> A BDMA hardware reference design is available

<sup>&</sup>lt;sup>15</sup> A IDMA hardware reference design is available

<sup>&</sup>lt;sup>16</sup> Appendix 6.1 explains how to retrieve a page in the provided file format in the case of IDMA loading.

<sup>&</sup>lt;sup>17</sup> This is a vendor dependent parameter. In the case of the TELINDUS modem, this retrain time out equals 24 seconds

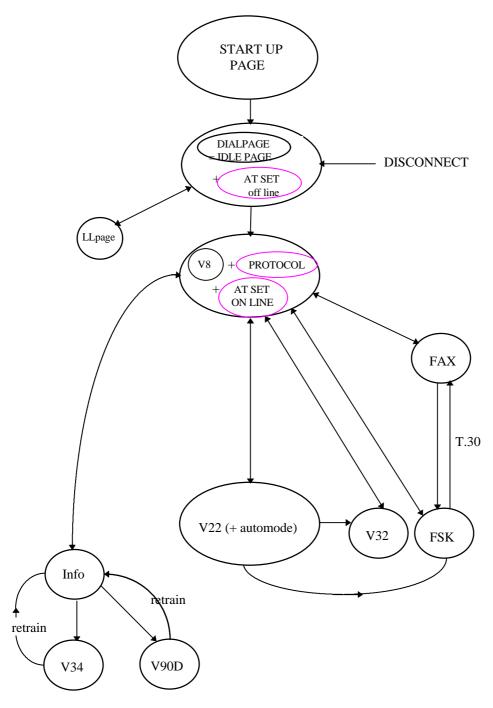

# 2.4. FLOW DIAGRAM OF BOOT SEQUENCE

In case of the modem software package the DIAL page also includes 'AT SET off line', they are booted simultaneously in one boot operation. Similarly the V.8 page includes PROTOCOL and 'AT SET on line'.

Figure 2 : boot operation flow diagram

# 3. LINE DRIVERS

# 3.1. INTRODUCTION

The DSP exchanges analogue samples with the line interface device through SPORT0.

## **Figure 3 : line interface**

Remark: In the case of PSTN applications, the ring signal enters the DSP through one of the flag-pins (PF0 .. PF7).

## 3.2. CODEC INTERFACES

## 3.2.1. AD1843 codec

DSP takes care of programming the CODEC and setting up the serial connection. This component can be used for all modulation types.

- Two drivers are available :

- daisy chain master driver

- daisy chain slave driver

## 3.2.2. AD1819 codec

DSP takes care of programming the CODEC and setting up the serial connection. This component can be used for all modulation types.

## 3.2.3. AD73311 codec

DSP takes care of programming the CODEC and setting up the serial connection. This component can be used for all modulation types up to V.32bis.

## 3.2.4. SGS-THOMSON STLC7545 codec

DSP takes care of programming the CODEC and setting up the serial connection. This component can be used for all modulation types.

## 3.3. T1 (E1) INTERFACE DEVICE

In the case of a T1 (E1) interface SPORT0 is programmed for multichannel operation and u-law or A-law companding.

The 5 sport0 multichannel control registers can be programmed by the user through the **SPORT0 setup** locations of the data-pump database.

| Sp0CntrlReg |

|-------------|

| Sp0MCRecL   |

| Sp0MCRecM   |

| Sp0MCTXL    |

| Sp0MCTXM    |

These locations are explained in chapter 5.3.1

# 4. HOST INTERFACE (MODEM SOFTWARE)

# 4.1. INTRODUCTION

The HOST processor has four tasks:

- Exchanging data packets. The SCC (Serial communication controller) interface is used for this task.

- **Controlling the modem**, for example: go off-hook, hang up connection, dial a number, channel selection, speed selection, selection of the error correction protocol, selection of the compression protocol, etc. All functions of the modem are controlled by **AT** <sup>(B)</sup> compatible commands.

- Loading software in the DSP 's memory<sup>18</sup>

- **configuration** of the system

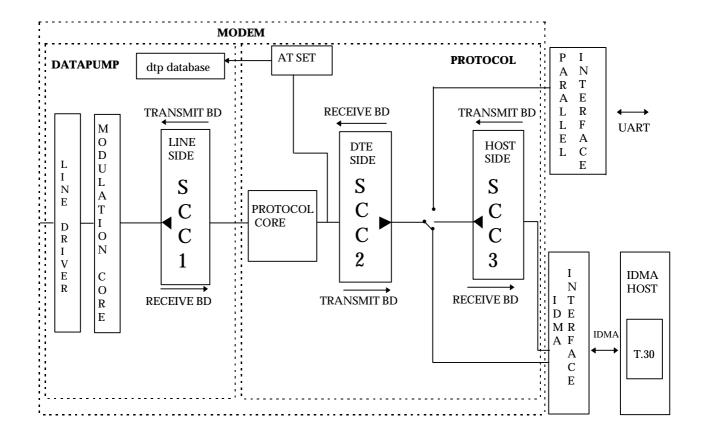

## 4.1.1. modem block diagram

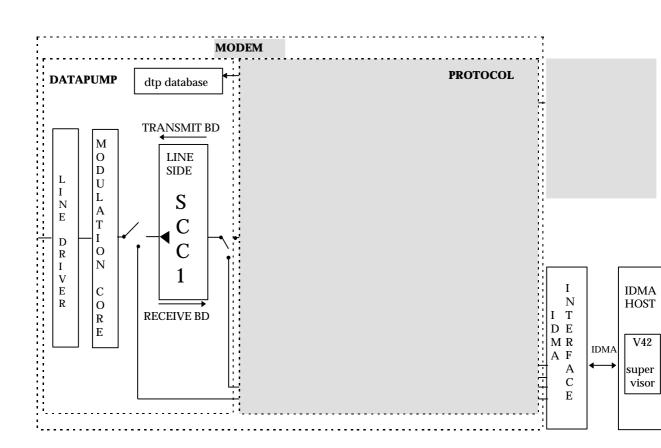

Figure 4 : modem block diagram

<sup>&</sup>lt;sup>18</sup> Only if the IDMA-loading method is applied.

naming conventions:

- SCC1 = DCE side SCC = LINE side SCC

- SCC2 = DTE side SCC

- SCC3 = HOST side SCC

- modem RX side buffers =

- data-pump RX buffers,

- DCE SCC RX buffers,

- DTE SCC TX buffers

- HOST SCC RX buffers

- modem TX side buffers =

- data-pump TX buffers,

- DCE SCC TX buffers,

- DTE SCC <u>**RX</u>** buffers</u>

- HOST SCC TX buffers

The user can interface to the modem via the **IDMA interface**<sup>19</sup>

4.1.2. data flow

The IDMA host can transfer data via

- a parallel asynchronous interface to V42 using the functionality of SCC2.

- a parallel asynchronous interface using the functionality of SCC3, which can handle asynchronous HDLC frames, used in asynchronous PPP connections. In this case data flow has to be configured. This is done in the location **DATACONFIG** (default=h#0000) of the data-pump write database. This location is explained in section 5.3.1

<sup>&</sup>lt;sup>19</sup> As shown in the block diagram a software configuration with an asynchronous data/control interface through a external UART component (16550) also is available. This configuration runs on a **demo-board.** A product which is at any time available for customer evaluation.

This interface uses the 16550 UART component, hooked up to the parallel bus of the ADSP2181 and placed in IO space. The interface always transfers **modem control** information to the AT set command interpreter. The AT set command interpreter updates the **modem database.** The AT commands can be used to configure the modem, when it is **off line** and **online**.

#### 4.1.3. control flow

Following sections explain the control operation for a system with IDMA HOST.

#### 4.1.3.1. The IDMA Interface

In the case of IDMA interface an essential part of the control flow **from DSP to host** is the **event generation**. The event mechanism is used to signal to the host whenever

- 1. the interface signals (CTS,DCD,DSR) change <sup>20</sup>

- 2. newly received information has filled buffers at modem RX side

- 3. Buffers have been emptied at modem TX side and should be filled

- 4. a boot operation is requested for IDMA download of a new page

Whenever the modem has new information available, it generates an event, i.e.

- it pushes an **event code** on the **event buffer**. The event buffer is an eight locations wrap around buffer. The event code specifies the kind of information available.

- it increments the **event counter**. The three LSB 's of this event counter are used as a wrap around write pointer for the event buffer. The pointer points to the last written position + 1 of the event buffer. The full 16 bit constitute a 16 bit wrap around counter counting the number of events. The host system has it's own event counter, pointing to the last read location + 1. If the difference between Host and DSP event counter is higher than eight, event information has been lost.

- it generates an event pulse using one of the DSP flags.

The host system can use the event system in polling or interrupt mode.

In polling mode the host regularly has to compare the DSP event counter with it's internal counter. Whenever there is a difference, it should read the event(s) from the event buffer. In interrupt mode the same operation should be triggered by a interrupt.

The status of the modem is maintained in two **memory mapped databases**, the **modem database** and the **data-pump database**. Although not essential for the operation of the interface from DSP to host, it can be useful for the host to read out the strapping and status of modem and data-pump.

In the case of IDMA interface, control flow from HOST to DSP is the memory mapped.

- This memory mapped interface is used to signal to the DSP whenever

- 1. if the interface signals (RTS,DTR) change <sup>21</sup>

- 2. Buffers have been emptied at modem RX side<sup>22</sup>

- 3. Buffers have been filled at modem TX side  $^{23}$

- 4. a boot operation is finished

- 5. to switch the system configuration from its default (in **DATACONFIG**)

On a regular basis the DSP checks the memory mapped interface and takes appropriate action.

<sup>&</sup>lt;sup>20</sup> through the **UARTMIRROR** registers of the MODEM database

<sup>&</sup>lt;sup>21</sup> through the register **DTESIGNALS** of the MODEM database

<sup>&</sup>lt;sup>22</sup> only for the DTE, DCE and HOST SCC interfaces, the data-pump interface assumes that the host reads (RX side) and writes (TX side) in time

<sup>&</sup>lt;sup>23</sup> identical remark

## 4.1.3.2. modem setup

The IDMA host always should transfer **modem control** information to the AT set command interpreter using the functionality of SCC2. The AT commands can be used to configure the modem, but only when it is **off line**.

The AT command set has three subtypes.

- General (Hayes standardised) AT commands. See section 4.3.1.2, 'General at\_set commands'.

- 'AT%s' commands : these commands update the %s registers. All these registers are grouped together and form the **AT modem database**. For more information see section 4.3.1.4, '%S Registers'.

- 'ATs' commands : these commands update the s registers. For more information see section 4.3.1.3, 'S-Registers'.

For the software package with host IDMA interface additional control information can be exchanged through IDMA setup and status locations. These setup locations are not accessible through AT set and only apply in the case of an IDMA system. Section 4.3.2, 'IDMA control interface' explains in detail.

No data-pump registers should be modified by the IDMA host. Two exceptions exist.

- 1. In the case of a T1/E1 interface the SPORT0 setup registers have to be initialised, see chapter 5.3.1

- 2. In the case the signal flow does not correspond to the default, the **DATACONFIG** register has to be changed. This register is explained in detail in section 5.3.1

## 4.1.3.3. modem status

The IDMA host always can request **modem status** information in two ways.

With the 'at%s?' command the user can read out the status of the '%s registers' through the AT set command interpreter using the functionality of SCC2, but only when the modem is **off line**. These registers are explained in more detail in chapter 4.3.1.4

For the software package with host IDMA interface additional status information of the protocols, modem and the connection can be derived from the IDMA status locations. These status locations are not accessible through AT set and only apply in the case of an IDMA system. Section 4.3.2, 'IDMA control interface' explains in detail.

## 4.2. DATA INTERFACE

#### 4.2.1. Introduction

The next sections give a general explanation of the SCC interface.

In following sections CP (communications processor) should be interpreted as

- for DTE side, SCC2 : Host

- for DCE side, SCC1 : DSP

- for HOST side, SCC3 : DSP user should be interpreted as :

- for DTE side, SCC2 : DSP(protocol or AT set)

- for DCE side, SCC1 : DSP(protocol ) or Host depending on DATACONFIG

- for Host side, SCC3 : HOST

For SCC1 and SCC2 the description of the buffer must be seen from the view of the V42, MNP or buffered mode. For SCC2 the bits are defined as used by these routines and it's the IDMA host who simulates the CP as if the SCC2 was transmitting the data to a serial interface. In this case, transmit BufferDescriptors are used to pass data to the host!

The SCC channel (SCC1 and SCC2) is described by the structure below, which can be accessed by IDMA. Most of these registers are used by the internal software.

struct SCC

{ word ModeReg; word nbits; word EventReg: word (\*TXState)(); void (\*RXState)(word data); word TotalBufCount; SCCBUFDESCRIP RXBufferDescriptor[MAXBUFDEF]; SCCBUFDESCRIP TXBufferDescriptor[MAXBUFDEF]; word Modereg2; word MaxBufLength; /\*maximum length of one buffer descriptions/ /\*receiving buffer offset 0,1,2..7\*/ /\*RBD\*/ word RXSCCBuffer; word RXSCCBufferOffset; /\*offset in the receive buffer ,1,2,...MaxBufLength/ word RXSCCBufferBitOffset; word RXSCCCRC; word RXWorkReg; word RXWorkReg1; word RXWorkReg2; word RXBreakLength; /\*transmitter buffer offset 0,1,2..7\*/ /\*TBD\*/ word TXSCCBuffer; word TXSCCBufferOffset; word TXSCCBufferBitOffset: word TXSCCCRC: word TXSCCCRC1; word TXBitsCalculated; word TXWorkReg; word TXWorkReg1; word TXWorkReg2; word \*TXPtr; word TXBreakLength; word XON1; word XON2; word XOFF1 word XOFF2 lword BreakAsyncReg; word BreakMask; word nbitsTx; };

The SCC tables below (for example section 4.2.3.1 for the UART SCC) give a more detailed explanation of each field of the structure and also indicate how they are accessed by the DSP and by the IDMA host.

Because the IDMA host and the DSP work asynchronously, there might be a problem when both the processors are using the same location at the same time.

For the **BufferDescriptor** fields it is bit 15 of the status location that indicates whether the host can use a BufferDescriptor or not. Bit 15 assures that the host and the DSP never operate on the same BufferDescriptor (and corresponding buffer). For the different SCCs the flow diagrams in their respective chapters explain in more detail the use of the bit 15.

For **all remaining locations** of the SCC structure, the problem is solved by the introduction of the event system. The protocol software only during initialisation writes the other fields of the list. For the EventReg and the ModeReg, this statement is true for the bits, which are relevant for the host. Whenever there has been a (re-)initialisation by the protocol software, the DSP generates an **initialisation event** to the host. The host has to do the following actions: 1. Read through IDMA the values of the fields of the SCC structure in the DSP.

## 2. Reinitialise its interface driver.

# 4.2.3. UART SCC

## 4.2.3.1. SCC structure

the base address of the DTESCCstructure can be found in the location DTESCCstructPtr of the modem IDMA database

The table below gives an overview of the usage of each field of the SCC structure by the protocol software, which runs on the DSP, and by the CP, running on the IDMA HOST.

| Off |  | IDN  | MA  | D    | SP   |

|-----|--|------|-----|------|------|

| set |  | hc   | ost | (pro | otoc |

|     |  | (CP) |     | ol   | ls)  |

|     |  | R    | W   | R    | V    |

| 0  | ModeReg                                                            |                          |                                                              | Χ |   | Χ | Σ |

|----|--------------------------------------------------------------------|--------------------------|--------------------------------------------------------------|---|---|---|---|

|    | D                                                                  | SENDBREAK                | if bit set SCC sends break and clears bit (only useful for   |   |   |   |   |

|    |                                                                    |                          | SCC1), the break time is placed inTXBreakLength              |   |   |   |   |

|    | В                                                                  | FLOWCONTROL              | 1 : enables XON/XOFF flow control (only useful for SCC1)     |   |   |   |   |

|    |                                                                    | XON/XOFF                 |                                                              |   |   |   |   |

|    | А                                                                  | SENDXOFF                 | if bit set SCC sends XOF and clears bit (only useful for     |   |   |   |   |

|    |                                                                    |                          | SCC1)                                                        |   |   |   |   |

|    | 9 SENDXON if bit set SCC sends XON and clears bit (only useful for |                          |                                                              |   |   |   |   |

|    |                                                                    |                          | SCC1)                                                        |   |   |   |   |

|    | 8                                                                  | V14                      | 1 : use V14 syasy (must be set only for SCC 1 in async mode) |   |   |   |   |

|    | 7,                                                                 | PARITY                   | 0 : no parity                                                |   |   |   |   |

|    | 6,                                                                 |                          | 1: odd parity                                                |   |   |   |   |

|    | 5                                                                  |                          | 2 : even parity                                              |   |   |   |   |

|    |                                                                    |                          | 3 : space parity                                             |   |   |   |   |

|    |                                                                    |                          | 4 : mark parity                                              |   |   |   |   |

|    |                                                                    |                          |                                                              |   |   |   |   |

|    | 4                                                                  | ASYNC BITS               | 0 : 7 data bits                                              |   |   |   |   |

|    |                                                                    |                          | 1 : 8 data bits                                              |   |   |   |   |

|    | 2                                                                  | ENT                      | 1 : enable transmitter                                       |   |   |   |   |

|    |                                                                    | 3 ENR 1: enable receiver |                                                              |   |   |   |   |

|    | 1,                                                                 | MODE                     | 0 : HDLC (only possible for SCC1)                            |   |   |   |   |

|    | 0                                                                  |                          | 1 : async                                                    |   |   |   |   |

| 1  | Nbits                                                              |                          | number of bits of a symbol. For the DTE interface, this      | Х |   |   | 2 |

|    |                                                                    |                          | number is fixed to 16 since the host is writing words to the |   |   |   | ĺ |

|    |                                                                    |                          | DSP                                                          |   |   |   |   |

| 2  | EventReg                                                           |                          |                                                              |   |   |   | 2 |

| 3  | TXState                                                            |                          | state variable of the CP transmitter                         | Х | Χ |   |   |

| 4  | RXState                                                            |                          | state variable of the CP receiver                            | Х | Χ |   |   |

| 5  | TotalBuf Co                                                        | ount                     |                                                              | Х | Χ |   |   |

| 6  | RXBufferD                                                          | escriptor[8*3]           | Data associated with the SCC receiver is stored in buffers.  | Х | Х | Х | 2 |

|    |                                                                    |                          | Each buffer is referenced by a BufferDescriptor(BD). BD's    |   |   |   | ĺ |

| 1D |                                                                    |                          | are located in a BD array. The BD array allows to define up  |   |   |   | ĺ |

|    |                                                                    |                          | to eight buffers for each channel.                           |   |   |   |   |

|    |                                                                    | -                        |                                                              |   |   |   |   |

|    | offset 0                                                           | STATUS AND               |                                                              |   |   |   |   |

|    |                                                                    | CONTROL                  |                                                              |   |   |   |   |

|    | offset 1                                                           | DATA LENGTH              |                                                              |   |   |   |   |

|    | offset 2                                                           | DATA BUFFER              |                                                              |   |   |   |   |

|    |                                                                    | POINTER                  |                                                              |   |   |   |   |

| 1E       | TXBufferD                         | escriptor[8*3]         | Data associated with the SCC transmitter is stored in buffers.                                                                                                                                                                                                                                                                                                                                                | Х        | X | Х | 2        |

|----------|-----------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|---|----------|

| <br>35   |                                   |                        | Each buffer is referenced by a BufferDescriptor(BD). BD's are located in a BD array. The BD array allows to define up to eight buffers for each channel .                                                                                                                                                                                                                                                     |          |   |   |          |

|          | offset 0                          | STATUS AND<br>CONTROL  |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

|          | offset 1                          | DATA LENGTH            |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | F        |

|          | offset 2                          | DATA BUFFER<br>POINTER |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

| 36       | Modereg2                          |                        | indicates the number of buffers and the character operation<br>mode of the buffers                                                                                                                                                                                                                                                                                                                            |          |   |   |          |

|          | F                                 | SPARE                  |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | ┢        |

|          | 4                                 |                        |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

|          | 4                                 | CharMode               | <ol> <li>all buffers operate with two characters per location</li> <li>all buffers operate with one character per location</li> <li>default charmode = 0</li> </ol>                                                                                                                                                                                                                                           |          |   |   |          |

|          | 3 NbrofBufs<br><br>0 MaxBufLength |                        | indicates the number of transmit buffers and receive<br>buffers.The default number of the RX and TX data buffers is<br>initialised by the modem software to :<br>default number = 6.                                                                                                                                                                                                                          |          |   |   |          |

| 37       | MaxBufLen                         | l<br>Igth              | the maximum length of an RX or TX buffer.<br>The default size of the RX and TX data buffers is initialised<br>by the modem software to :<br>default size=40 memory locations.                                                                                                                                                                                                                                 | X        |   |   | 2        |

| 38       | RXSCCBuf                          | fer                    | indicates in which BufferDescriptor the receiver CP is writing data                                                                                                                                                                                                                                                                                                                                           | Х        | Х |   | 2        |

| 39       | RXSCCBuf                          | ferOffset              | indicates which is the last received character in the current<br>BufferDescriptor, even when the buffer is not closed.                                                                                                                                                                                                                                                                                        | Х        | Х | Х | Σ        |

| 3A       | RXSCCBuf                          | ferBitOffset           |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

| 3B       | RXSCCCR                           |                        |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

| 3C       | RXWorkRe                          | •                      |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | <b> </b> |

| 3D       | RXWorkRe                          | *                      |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | +        |

| 3E<br>3F | RXWorkRe<br>RXBreakLe             | *                      |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | +        |

| 40       | TXSCCBuf                          |                        | indicates from which BufferDescriptor the transmitter is                                                                                                                                                                                                                                                                                                                                                      | X        | X |   | Σ        |

| 41       | TXSCCBuf                          | ferOffset              | sending data<br>indicates how many characters in the buffer already are<br>transmitted                                                                                                                                                                                                                                                                                                                        | X        | X |   | Σ        |

| 42       | TXSCCBuf                          | ferBitOffset           |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | $\vdash$ |

| 43       | TXSCCCR                           | С                      |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

| 44       | TXSCCCR                           |                        |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   |          |

| 45       | TXBitsCalc                        |                        |                                                                                                                                                                                                                                                                                                                                                                                                               | Χ        | Х |   | 2        |

| 46       | TXWorkRe                          | 0                      |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | $\vdash$ |

| 47<br>48 | TXWorkRe                          |                        |                                                                                                                                                                                                                                                                                                                                                                                                               |          |   |   | <u> </u> |

| 48<br>49 | TXWorkRe<br>TXPtr                 | <u>g</u> 2             |                                                                                                                                                                                                                                                                                                                                                                                                               | X        | X |   | +        |

| 49<br>4A | TXBreakLe                         | ngth                   | If the SENDBREAK bit is set in ModeReg the transmitter<br>will send a break for a time as indicated by TXBreakLength<br>(1 unit is 416 uS(= 1/2400))<br>(not supported)                                                                                                                                                                                                                                       | <u> </u> | Λ |   |          |

| 4B       | XON1                              |                        | Define the xon character. Two xon characters can be<br>specified on which the transmitter will restart transmission.<br>If one of these characters are not used, the highest bit of the<br>word has to be set. Flow control with the parallel interface of<br>SCC2 has no sense because there is no serialising of the data<br>and the flow control are regulated by not reading the data.<br>(not supported) |          |   |   |          |

| 4C | XON2              | Defines the second xon character  |  |  |

|----|-------------------|-----------------------------------|--|--|

|    |                   | (not supported)                   |  |  |

| 4D | XOFF1             | Defines the first xoff character  |  |  |

|    |                   | (not supported)                   |  |  |

| 4E | XOFF2             | Defines the second xoff character |  |  |

|    |                   | (not supported)                   |  |  |

| 4F | BreakAsyncRegHigh |                                   |  |  |

| 50 | BreakAsyncRegLow  |                                   |  |  |

| 51 | BreakMask         |                                   |  |  |

| 52 | nbitsTx           | not in use                        |  |  |

Table 3 : SCC2 structure for UART operation

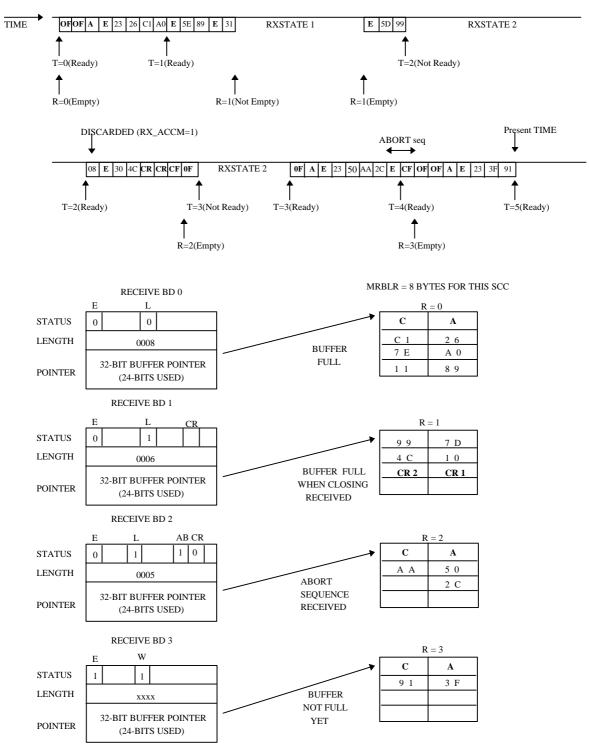

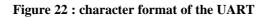

#### 4.2.3.2. UART receive BufferDescriptor (RXbd)

The CP reports information about each buffer of received data by its BDs. The RX BD is shown in figure 5. The CP closes the current buffer, generates a maskable interrupt and starts to receive data in the next buffer due to any of the following events:

- 1. Detection of an error during message processing

- 2. Detection of a full received buffer

- 3. Reception of a programmable number of consecutive IDLE characters.

|           | 15 | 14                | 13 | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5  | 4  | 3  | 2 | 1 | 0 |

|-----------|----|-------------------|----|----|----|----|---|----|---|---|----|----|----|---|---|---|

| OFFSET +0 | Е  | -                 | W  | Ι  | -  | -  | - | ID | - | - | BR | FR | PR | - | - | - |

| OFFSET +2 |    | DATA LENGTH       |    |    |    |    |   |    |   |   |    |    |    |   |   |   |

| OFFSET +4 |    | RX BUFFER POINTER |    |    |    |    |   |    |   |   |    |    |    |   |   |   |

#### Figure 5 : UART Receive BufferDescriptor

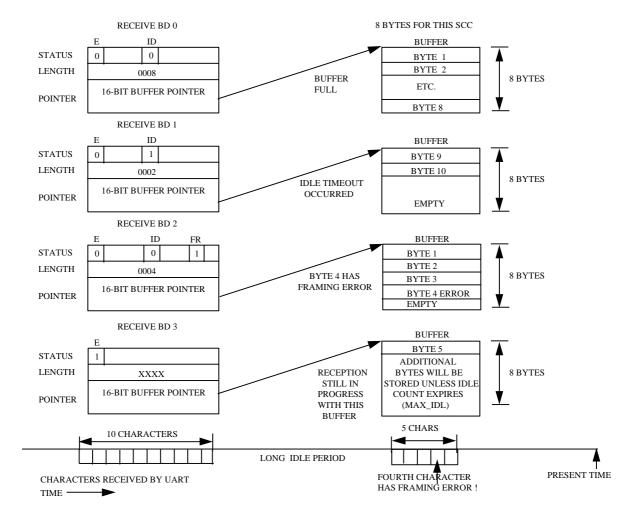

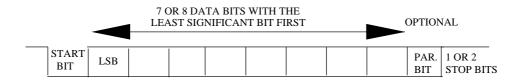

An example of the UART receive process is shown in figure 6. This shows the resulting state of the RX BDs after receipt of 10 characters, an idle period and five characters - one with a framing error. The example assumes that MaxBufLength = 8 in the SCC parameter RAM.

Figure 6 : UART RX BD Example

#### control and status bits.

#### E - Empty

- 0 = The data buffer associated with this BD has been filled with received data, or data reception has been aborted due to an error condition. The user is free to examine or write to any fields of the BD.

- 1 = The data buffer associated with this BD is empty. This bit signifies that the BD and its associated buffer are available to the CP. The user should not write to any fields of this BD after it sets this bit. The empty bit will remain set while the CP is currently filling the buffer with received data.

#### W - Wrap (Final BD in Table)

0 = This is not the last BD in the RX BD table.

1 = This is the last BD in the RX BD table. After this buffer has been used, the CP will receive incoming data into the first BD in the table, allowing the user to use fewer than eight BDs to conserve internal RAM.

#### NOTE

The user is required to set the wrap bit in one of the first eight BDs; otherwise, errant behavior may occur.

#### I = Interrupt(does not apply)

0 = No interrupt is generated after this buffer has been filled.

1 = The RX bit in the UART event register will be set when this buffer has been completely filled by the CP.

The following bits contain status information written by the CP after it has finished receiving data in the associated data buffer.

#### ID - Buffer closed on reception of idles(does not apply)

The buffer was closed due to the reception of the programmable number of consecutive IDLE sequences.

#### BR - Break Received

A break sequence was received. The break length is indicated by the data length field.

#### FR - Framing Error(does not apply)

A character with a framing error was received and is located in the last byte of this buffer. A framing error is detected by the UART controller when no stop bit is detected in the receive data string.

#### PR - Parity Error(does not apply)

A character with a parity error was received and is located in the last byte of this buffer.

#### Data Length

The data length is the number of octets written to this BD's data buffer. It is written by the CP once as the BD is closed.

#### **RX Buffer Pointer**

The receive buffer pointer points to the first location of the associated data buffer.

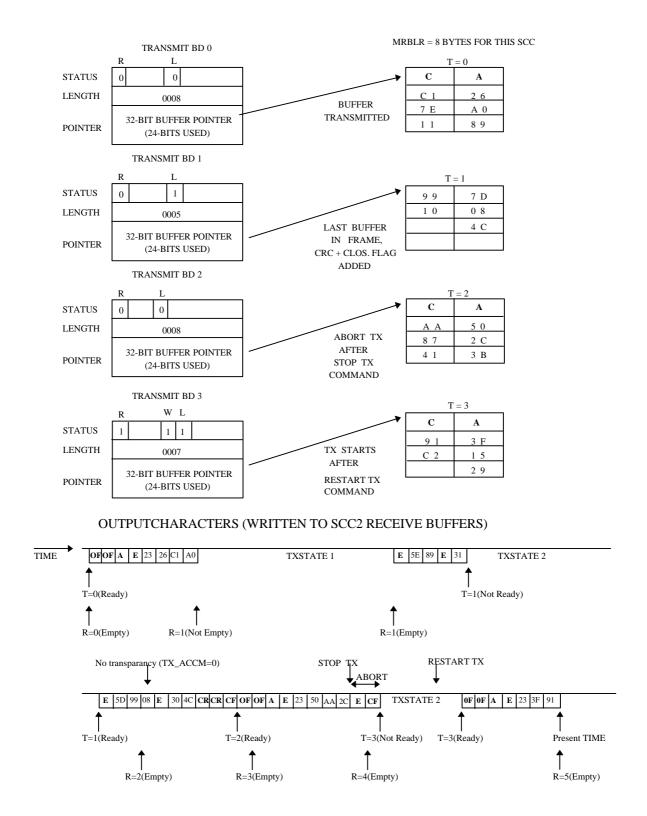

## 4.2.3.3. UART transmit BufferDescriptor (TX bd)

Data is presented to the CP for transmission on an SCC channel by arranging it in buffers referenced by the channel's TX BD table.

|           | 15 | 14                | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----|-------------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| OFFSET +0 | R  | Х                 | W  | Ι  | -  | -  | - | - | - | - | - | - | - | - | - | - |

| OFFSET +2 |    | DATA LENGTH       |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| OFFSET +4 |    | TX BUFFER POINTER |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

#### Figure 7 : UART Transmit BufferDescriptor

The first word of the TX BD contains status and control bits. The following bits are prepared by the user before transmission and set by the CP after the frame has been transmitted.

#### R - Ready

- 0 = This buffer is not currently ready for transmission. The user is free to manipulate this BD (or its associated buffer). The CP clears this bit after the buffer has been transmitted or after an error condition has been encountered.

- 1 = The data buffer, which has been prepared for transmission by the user, has not been transmitted or is currently transmitting. No fields of this BD may be written by the user once this bit is set.

#### I - Interrrupt

0 = No interrupt is generated after this buffer has been serviced.

1 = The TX bit in the UART event register will be set when this buffer has been serviced by the CP, which can cause an interrupt.

Bits 8 - 1 - Reserved for future use.

#### Data Length

The data length is the number of octets that the CP should transmit from this BD's data buffer. It is never modified by the CP. This value should be normally greater than zero. The data length may be equal to zero with the P bit set and only a preamble will be sent.

#### TX Buffer Pointer

The transmit buffer pointer points to the first location of the associated data buffer and may be even or odd. The buffer may reside in either internal or external memory.

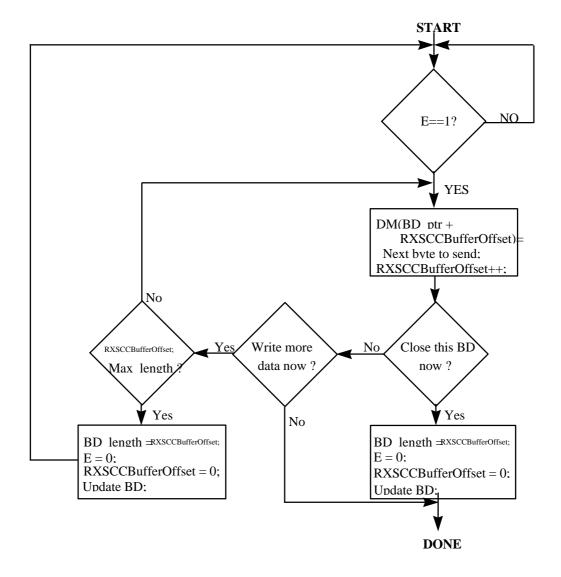

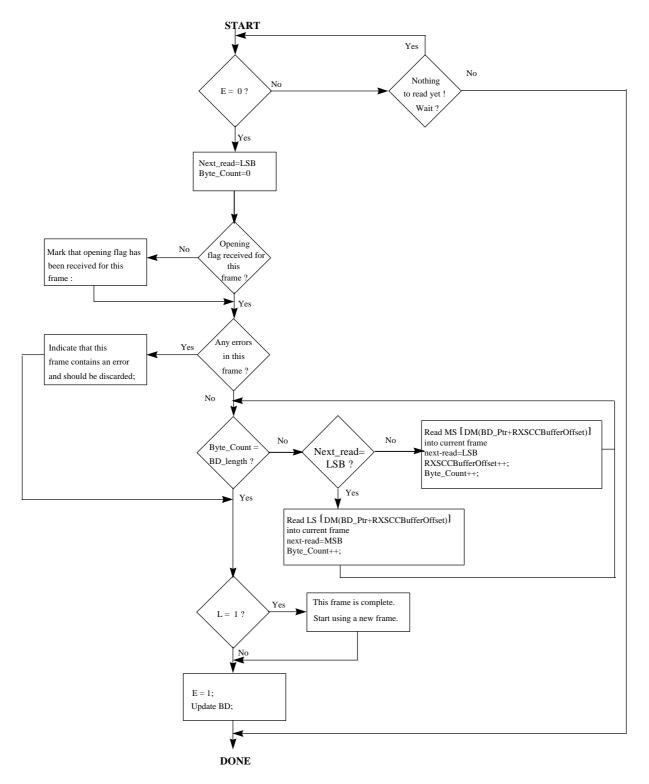

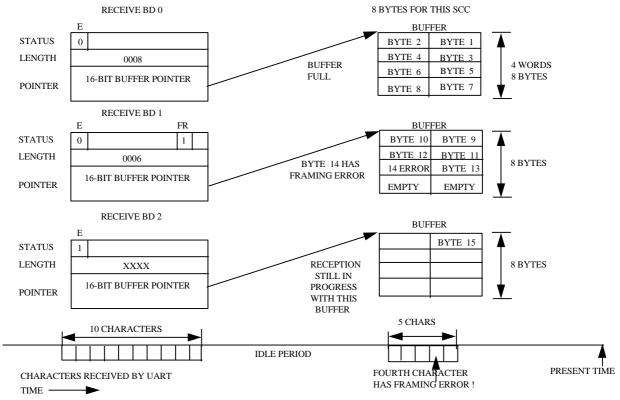

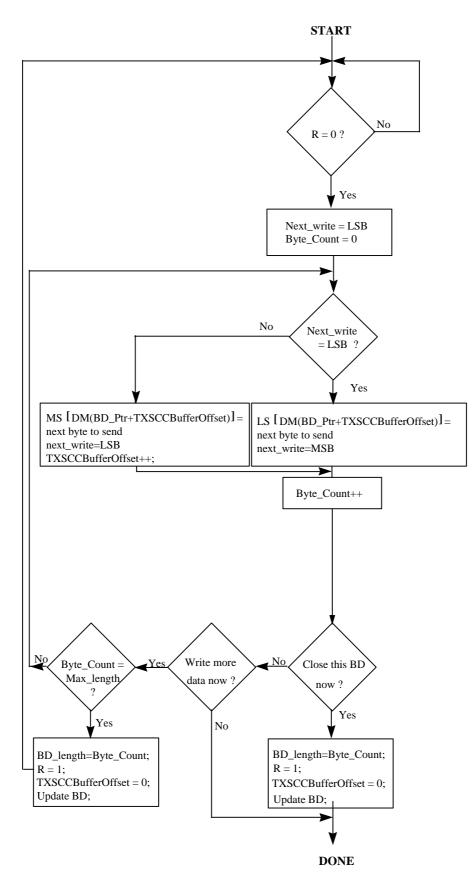

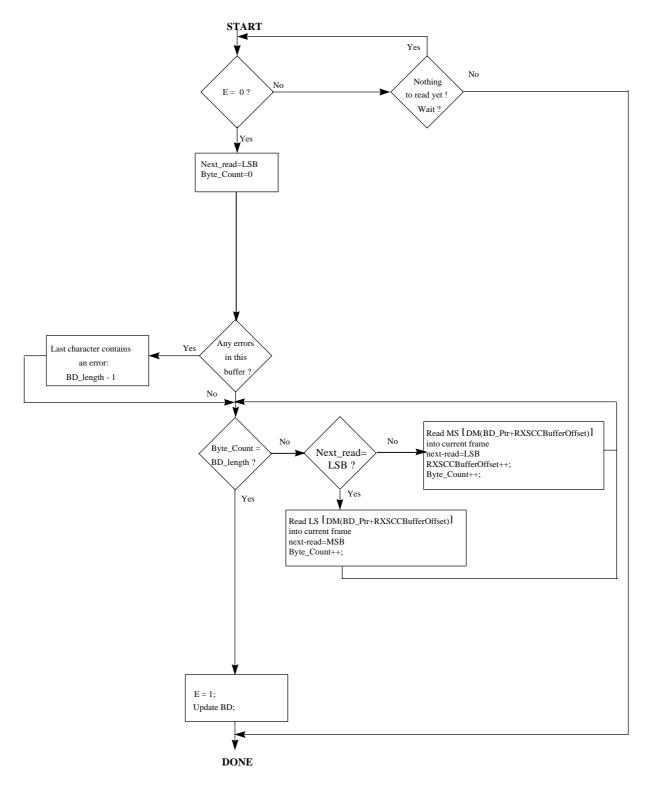

## 4.2.3.4. IDMA - SCC2 receiver interaction

This flow diagram below gives an example of how an IDMA host driver could interface with the DTE SCC structure .

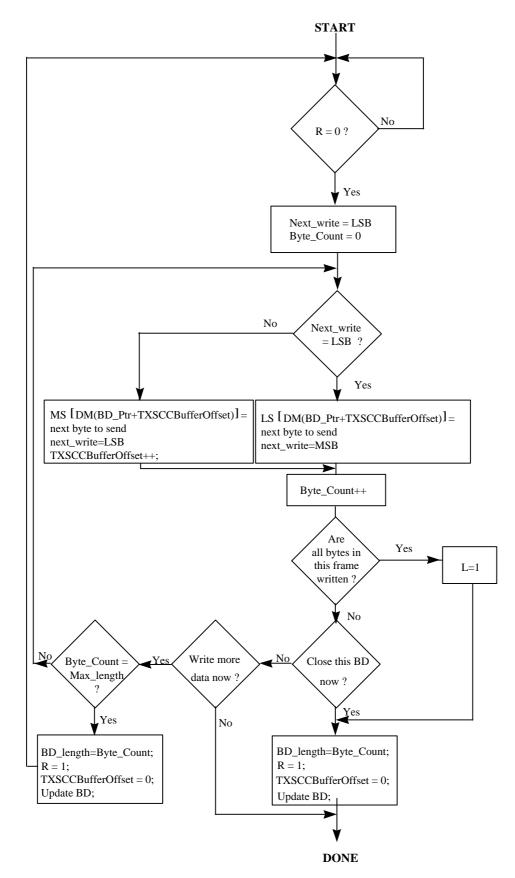

Figure 8 : flow diagram of interaction between SCC2 receiver and the IDMA host

SCC2 is directed towards the IDMA HOST, i.e. when the IDMA HOST wants to write to SCC2 (e.g. an AT-command) it will use the receive buffers in SCC2 (acting as CP)

The IDMA HOST has a variable containing currently used BufferDescriptor (BD). This variable (called BD in the flow chart) is initialised to buffer no. 0. When this variable is updated the buffer no. is incremented by 1 until it reaches  $6^{24}$ , then it is set to 0 again. The IDMA HOST must always check that the E bit in the current BD is set (1) before it can start modifying the BD or its data. The DSP will set (1) this bit when it has read the data.

The sequence which the IDMA HOST should follow when writing to SCC2 is described in the flow chart in Fig.8. (*describes the case of Polling mode*)

<sup>&</sup>lt;sup>24</sup> The number of buffers is not fixed. The IDMA host should check the wrap bit in the BufferDescriptor, at least after initialisation of the SCC structure, to know the number of buffers

Remarks:

1. The 'start' task can be interrupt triggered by an incoming event indicating a buffer is empty

2. In interrupt triggered operation, checking the empty bit is allowed but not required, if the bit is not set it would indicate an error condition. Equally initiating a wait loop in not required.

3. test 'close this BD now', if 'yes' it also implies you want to terminate.

4. test 'write more data now' if 'no', next time the flow diagram is executed, the 'start' task should immediately jump to this test again to have error free behaviour

5. in case of interrupt triggered operation the test on 'Max\_length', if 'yes', flow could return to the 'yes' output of the 'close BD now' test

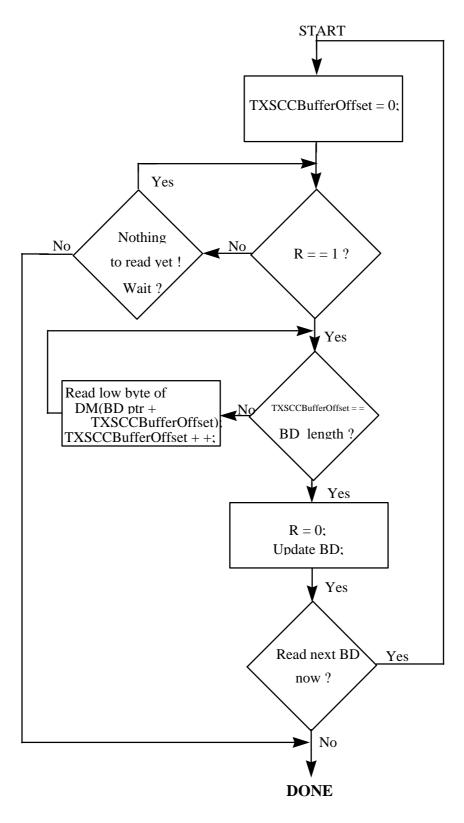

This paragraph describes a flow diagram that could be used as an example for the host driver interacting with the DTE SCC transmitter

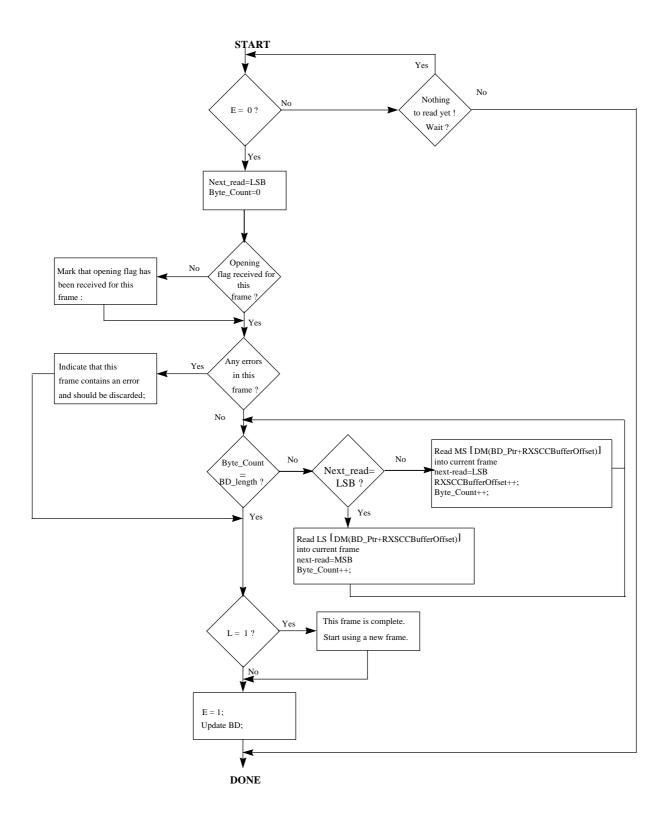

Figure 9 : flow diagram of interaction between SCC2 transmitter and the IDMA host

SCC2 is directed towards the IDMA HOST, i.e. when the IDMA HOST want to read from SCC2 (e.g. modem data without PPP) it will use the transmit buffers in SCC2 (acting as CP).

The IDMA HOST has a variable containing the current BufferDescriptor (BD) to read from. This variable (called BD in the flow chart) is initialised to buffer no. 0. When this variable is updated the buffer no. is incremented by 1 until it reaches  $6^{25}$ , then it is set to 0 again. The IDMA HOST must always check that the R bit in the current BD is set (1) before it can start modifying the BD or its data.

The IDMA HOST clears (0) this bit when all data has been read. The DSP sets this bit in the BufferDescriptors that are ready to be read from the IDMA HOST.

The sequence which the IDMA HOST should follow when reading from SCC2 is described in the flow chart in Fig.3. *(describes the case of Polling mode)*

#### Remarks:

1. the 'START' task can be interrupt triggered by an incoming event, indicating a new buffer is full

2. in interrupt triggered operation, checking the ready bit is allowed but not required, if the bit is not set it would indicate an error condition. Equally, initiating a wait loop is not required

3. in the case of interrupt driven operation the test ' read next BufferDescriptor now' would become obsolete because part of the 'START' task.

<sup>&</sup>lt;sup>25</sup> The number of buffers is not fixed. The DP should check the wrap bit in the BufferDescriptor, at least after initialisation of the SCC structure, to know the number of buffers

# 4.2.4. Asynchronous HDLC SCC

An Async HDLC module, situated in SCC3 may be activated. The functionality of the module is limited to what is required for running the async PPP protocol :

- \*Automatic 16-bit CRC generation and checking (CRC-CCITT)

- \*Automatic generation of opening and closing flags

- \*Reception of frames with only one "shared" flag

- \*Automatic generation and stripping of transparency characters according to RFC 1549 utilising transmit and receive control character maps.

- \*Transparent transmission of characters equal to the opening flag, closing flag or escape character.

- \*Automatic transmission of the ABORT sequence (escape character, closing flag) and closing of the current transmitbuffer after the STOP TRANSMIT command is issued by the user.

- \*Automatic transmission of the next transmitbuffer after the RESTART TRANSMIT command is issued by the user.

- \*Closing the current receivebuffer and waiting for the next frame after reception of the ABORT sequence.

Configuration of the Async HDLC consists of the definition of the Openflag Character, the Closingflag Character, the Escape Character, the Number of Opening Flags and the transmit and receive character maps. For all of these parameters locations are provided in the Async HDLC database.

## Async HDLC database

The Baseaddress of the database can be found in the location ACCM map address of the modem read database.

| 0 | TX_ACCM : Transmit Async Control Character Map | (LSW) | Initial Value FFFF | write |

|---|------------------------------------------------|-------|--------------------|-------|

| 1 | TX_ACCM : Transmit Async Control Character Map | (msw) | FFFF               | write |

| 2 | RX_ACCM : Receive Async Control Character Map  | (LSW) | FFFF               | write |

| 3 | RX_ACCM : Receive Async Control Character Map  | (msw) | FFFF               | write |

| 4 | openflag_ch                                    |       | 7E                 | write |

| 5 | closingflag_ch                                 |       | 7E                 | write |

| 6 | escape_ch                                      |       | 7D                 | write |

| 7 | nmbr_of_openflags (0 : Shared Flag Option)     |       | 1                  | write |

Table 4 : Async HDLC database

## 4.2.4.1. The SCC structure

the base address of the HOSTSCCstructure can be found in the location HOSTSCCstructPtr of the IDMA modem read database.